高精度小抖动脉冲延时发生器的研制  下载: 579次

下载: 579次

1 引 言

像增强器、条纹管等由于其超快的响应速度和超高时间分辨率广泛应用于距离选通激光雷达和三维成像激光雷达[1]。距离选通激光雷达可实现不同距离回波信号的选通成像[2],像增强器的选通响应时间不足10 ns,这意味着同步触发信号的延时精度和抖动精度需要达到亚ns级才能确保探测图像的完整性和准确性。三维成像激光雷达是通过高速扫描电压将不同时刻返回的回波信号在空间上进行展开得到目标的轮廓信息[3],而扫描电压全程扫描时间最快为ns甚至亚ns,这就要求同步触发信号的延时精度和抖动精度要达到几十ps量级才能保证探测图像的完整和准确。因此,研制一款高精度小抖动的脉冲延时发生器来满足激光雷达高性能同步要求具有重要的现实意义。

目前世界上对于高精度小抖动脉冲延时发生器的研究属美国斯坦福大学研制的数字延时信号发生器 DG645性能尤为突出,有四个独立通道,延时分辨率可达5 ps,信号抖动范围50 ps,但DG645体积大,无法满足激光雷达小型化要求。国内在脉冲延时技术的研究领域也开展了很多工作[4,5,6],但相关性能与国外相比仍存在差距。文章针对脉冲延时的精度和抖动问题展开分析和研究,设计和研制了一款高精度小抖动脉冲延时发生器,并对发生器进行了测试。

1 脉冲延时发生器总体方案

1.1 随机抖动消除机理

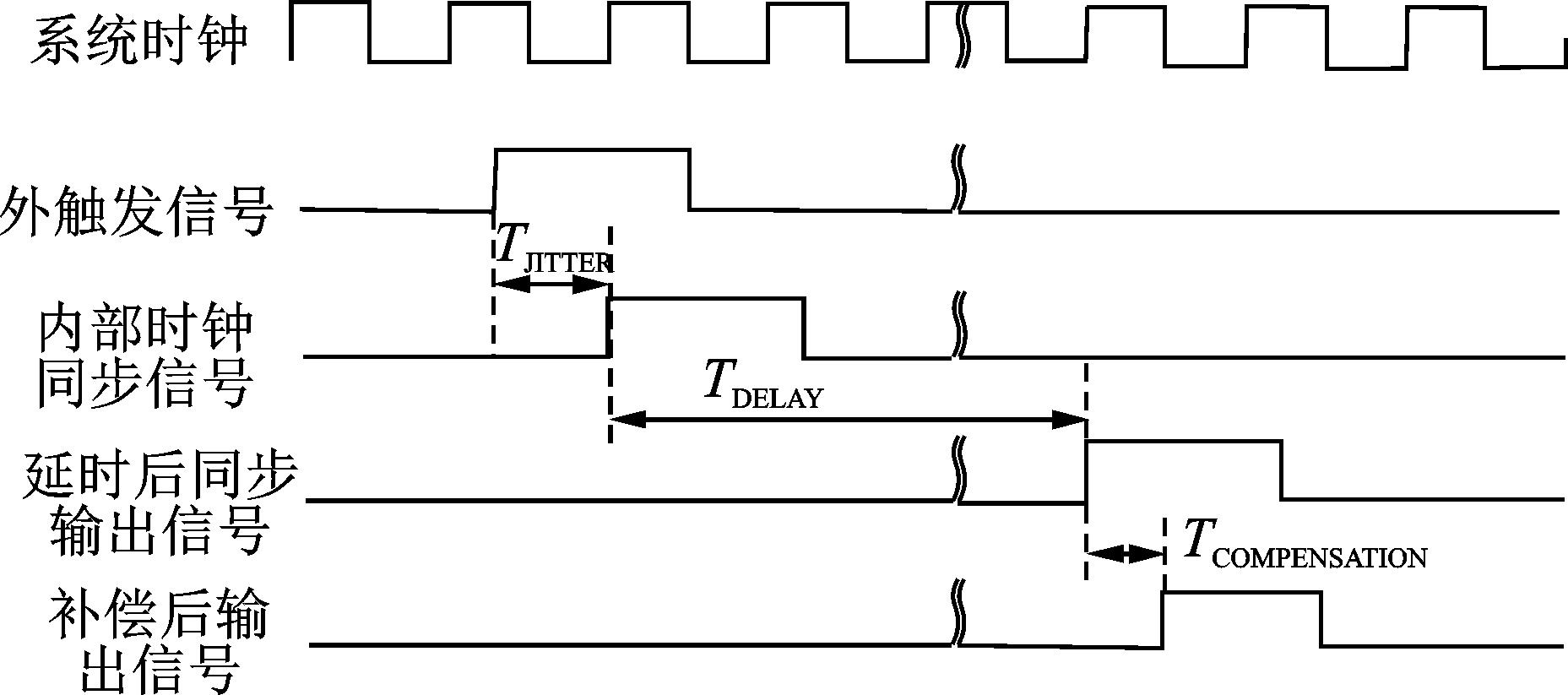

目前常用的脉冲延时方案主要是数字计数与模拟延时芯片相结合的方案。该方案特点是延时范围大,延时精度高,但外触发信号和系统同步时钟之间的抖动TJITTER没有解决。TJITTER相对于系统同步时钟是随机的,若能将每一次的TJITTER测量并保存下来,在设定延时TDELAY完成时额外增加一个补偿时间TCOMPENSATION,使得TJITTER和TCOMPENSATION关系满足

1.2 脉冲延时发生器总体方案

利用抖动补偿的消抖技术,采用数字计数延时和模拟延时相结合的方案可以满足高精度小抖动的要求,其总体方案如下:以通道AB为例, FPGA通过485串口接收上位机传来的延时和脉宽数据,将延时数据的10 ns(系统时钟100 MHz)的整数倍配置到计数A寄存器,剩余10 ns以下部分经SPI总线配置给用于模拟延时的数模转换器(DA)A,同样,FPGA将脉宽数据分别配置给计数B寄存器和数模转换器B。当外触发信号到来时,其工作流程如

整个系统采用12 V供电,485串口通信,4通道独立输出。FPGA不单作为数字计数延时,也是整个系统的控制核心,通过对各功能模块DA参数设置保证其工作在正确状态;通过接受串口指令可对触发模式(内触发或外触发)、内触发频率、脉冲输出使能、脉冲输出极性进行设置。

2 脉冲延时发生器设计

2.1 抖动测量保持电路设计

抖动测量保持电路采用的是电流积分技术,其原理是利用恒流源在TJITTER期间对电容充电将随机时间值转换为随机电压值,并将该电压进行保持。其原理如

恒流源输出精度和稳定性、充电电容容量稳定性以及电压损耗稳定性、开关的开通关断速度是影响抖动测量保持电路准确性和稳定性的主要因素,其中,开关的开通关断能力是关键。

文中开关电路采用的是发射极耦合(ECL)开关电路。传统的TTL工作在截止区和饱和区,当信号从饱和区进入截止区时,由于三极管集电极结电容较大,无法快速放电,使得TTL无法工作在高速场合。而ECL只工作在放大区和截止区,因此ECL电流开关速度很快,其延时可达纳秒甚至亚纳秒。ECL电流开关电路如

电容上电压充电速率V如

2.2 数字计数延时设计

数字计数延时是利用FPGA时钟计数实现的,外触发信号到来时,抖动测量保持电路产生同步触发信号,触发FPGA按照时钟频率开始计数,当计数值到达设定值(延时时钟周期的整数倍部分)时,停止计数并输出计数结束信号作为抖动补偿的触发信号。设需要延时的时间为t,计数设定值为N,计数时钟周期为T,则计数器设定值的计算表达式如

考虑到延时脉冲为4通道独立输出,每路通道的延时和脉宽单独调节,因此需要设计八路数字计数延时模块。

2.3 抖动补偿和模拟延时设计

抖动补偿和模拟延时电路主要实现功能有:1、利用VJITTER实现抖动补偿,消除随机抖动;2、完成同步计数周期以内的3 ps分辨率时间延时。

2.3.1 抖动补偿设计

抖动补偿电路的原理是数字计数延时完成时额外增加一个补偿延时TCOMPENSATION,使得TJITTER+TCOMPENSATION为一常数,消除随机抖动。该原理反映到电路上如

等效开关S3是由D触发器和比例运放构成的,其电路如

电容上电压放电速率可参照

假设数字计数设定值为N,计数时钟周期为T,不考虑模拟延时,则输出脉冲总延时t也为常数,如

2.3.2 模拟延时设计

模拟延时电路原理是在抖动补偿电路的基础上将模拟延时值转化为抖动补偿电容起始电平VI,通过对VI的调节,实现TCOMPENSATION的调节,最终实现模拟延时的微调,其原理如

设计数时钟周期为T,模拟延时为τ,随机抖动电压变化范围δ,则抖动补偿电容起始电平VI可以用

起始电平VI的设置,可以通过DA实现,以时钟周期10 ns为例,采用12 bit DA,则模拟延时的分辨率理论值σ=10 ns/212=2.44 ps,能够满足3 ps的要求。

2.4 通道同步一致性设计

脉冲延时发生器各通道之间的输出信号同步通过输入信号同步和时钟分配实现,如

3 脉冲延时发生器实物和测试

3.1 脉冲延时发生器实物展示

整个电路板采用8层结构单板设计,尺寸为150 mm×160 mm,相比较同类脉冲延时发生器,尺寸已大幅度缩小,更符合激光雷达小型化的要求。

3.2 脉冲延时发生器测试

对脉冲延时发生器进行了整体性能测试,使用DG645作为外触发信号源,频率设置为1 kHz,脉宽100 ns,跳变时间小于2 ns,输出电平为2.5 V@50 Ω;使用带宽为6 GHz的LeCroy 8600A示波器对发生器进行测试。测试项目包括抖动和模拟延时两部分,抖动测试内容包括零延时输出与外触发信号之间的抖动和100 s延时下的抖动;模拟延时测试内容包括不同模拟延时设置时的输出延时情况和最小延时分辨率。

3.2.1 脉冲延时发生器抖动测试

输出与外触发信号之间抖动测试过程如下:将DG645设置成内触发模式,输出两路同步信号,一路作为延时脉冲发生器的触发输入,一路作为发生器输出信号的延时参照信号。发生器工作在默认状态,以AB通道为例,延时为本底零延时,脉宽为100 ns。用示波器测试参照信号与发生器输出信号之间的延时,进行1 000次记录并计算抖动时间。

图 10. 零延时输出与外触发抖动测试结果

Fig. 10. Test result of jitter between zero delay output and external trigger

100 s延时与零延时抖动测试过程一致,为了方便测试以及保证测试的准确性,将触发参照信号也进行100 s延时,使得输出信号和触发信号在较小的时间刻度时测试,其结果如

图 11. 延时100

Fig. 11. Test result of jitter between 100

3.2.2 脉冲延时发生器模拟延时测试

脉冲模拟延时测试过程与抖动测试过程一致,同样也对触发参照信号做了100 s延时处理,在100 s延迟的基础上进行模拟延时调节,测试模拟延时和最小延时分辨率,以AB通道为例,分别测试模拟延时设置为100 s(基准)、99.999 s(调节1 ns)、99.999 997 56 s(最小延时分辨率2.44 ps)时的延时情况,经过1000次测试记录,其测试结果如

表 1. 模拟延时测试数据

Table 1. 模拟延时测试数据

|

4 结 论

针对激光雷达高精度小抖动同步技术的需要,对脉冲延时的抖动和精度问题开展分析,确定了数字计数和模拟延时相结合的总体方案,采用抖动补偿技术实现消抖,模拟电路实现延时高精度。通过对脉冲延迟发生器的实际测试,延时抖动和精度分别小于40 ps和3 ps,与DG645性能参数相当,证明了该方案具有一定的先进性,能够满足激光雷达同步技术的高性能和小型化要求。

[1] 王梦宇,张延超,李美伦,等, 王梦宇,张延超,李美伦,等, 王梦宇,张延超,李美伦,等. 用于激光雷达的高精度脉冲延时及脉宽控制研究[J]. 机械与电子, 2016, 34(8): 3.

[2] 伍 伟,方盛江,迟 晨,等, 伍 伟,方盛江,迟 晨,等, 伍 伟,方盛江,迟 晨,等. 用于门控组件的高精度低抖动同步技术[J]. 光电子技术, 2019, 39(1): 43-44.

[3] AsherGelbart, AsherGelbart, AsherGelbart, Asher Gelbart, Redman BrianC, Redman BrianC, Redman BrianC, Redman Brian C, Light R S, LightR S, LightR S, LightR S. Flash lidar based on multiple-slit streak tube imaging lidar[J]. Proc. SPIE., 2002, 4723: 9-11.

[4] 张 锋,欧阳娴,刘百玉,等, 张 锋,欧阳娴,刘百玉,等, 张 锋,欧阳娴,刘百玉,等. 用于超短激光脉冲技术的高精度数字同步机的研究[J]. 电子器件, 2007, 30(6): 2288-2290.

Article Outline

迟晨, 伍伟, 方盛江, 刘德林. 高精度小抖动脉冲延时发生器的研制[J]. 光电子技术, 2020, 40(2): 108. Chen CHI, Wei WU, Shengjiang FANG, Delin LIU. Development of a High⁃precision and Low⁃jitter Pulse Delay Generator[J]. Optoelectronic Technology, 2020, 40(2): 108.