High-density and wide-bandwidth optical interconnects with silicon optical interposers [Invited]  Download: 1070次

Download: 1070次

1. INTRODUCTION

The interchip bandwidths in personal computers and servers are doubling every two years [1]. Since, CPUs used for high-end servers currently have an overall interchip bandwidth of about 1.5 Tbps, which consists of 0.5 Tbps for the CPU–CPU interconnects, 0.4 Tbps for the memory, and 0.6 Tbps for the peripherals, the overall interchip bandwidth is expected to reach the 10-Tbps level by the late 2010s. Although the wiring pitches in logic circuits are expected to shrink exponentially in accordance with Moore’s law, LSI I/O pad pitches, such as flip-chip pad pitches, are presently expected to remain large scale [2]. This is why the line speed for interchip interconnects in the future needs to be much higher than that for intrachip ones. The required line speed is estimated to exceed 40 Gbps by the late 2010s, and currently there are no known solutions for manufacturing electrical interconnects that can supply this speed [2]. Optical interconnects with silicon photonics are potential candidates for solving the bandwidth bottleneck problem [1,3

In this paper, in order to solve the bandwidth bottleneck problem in interchip interconnects by using silicon photonics, we examine photonics–electronics integration and light source integration for interchip optical interconnects, propose a photonics–electronics convergence system with a silicon optical interposer fully integrated with optical components on a single silicon substrate, investigate optical components for the optical interposers, and demonstrate the feasibility of our system through data link experiments with the silicon optical interposers.

2. PHOTONICS–ELECTRONICS CONVERGENCE SYSTEM FOR INTERCHIP INTERCONNECTS

2.1 A. Integration between Photonics and Electronics

Because the performance of electrical interconnects generally declines with their distance more rapidly than does that of optical interconnects, it is important to place optical transceivers (E/O and O/E signal converters) as close to LSIs as possible for wide-bandwidth interchip interconnects with photonic wiring. Silicon photonics is the most suitable technology for these applications because of its compactness and compatibility with LSIs.

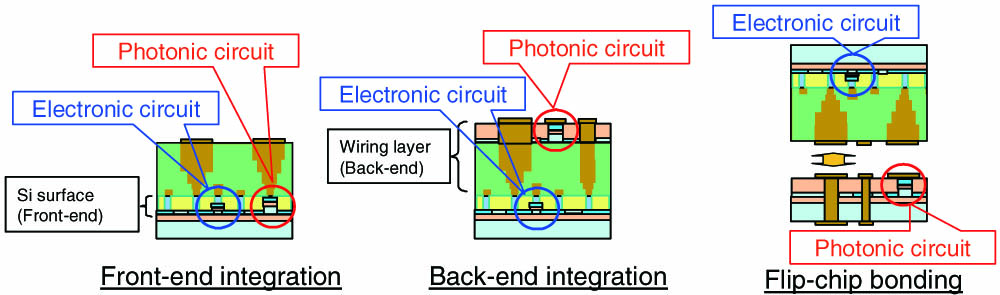

Generally, there are three types of integration between photonic and electronic circuits with silicon photonics as shown in Fig.

2.2 B. Light Source Integration

First, when considering the light source arrangement in our interchip optical interconnects, we had to choose between off-chip or on-chip sources. Although off-chip light sources are the more flexible of the two, they require highly precise optical connectors and care for polarization dependence to obtain optical power from the off-chip light sources into the substrate via optical fibers. Because we think that this is not practical for large scale interconnects, we have chosen on-chip light sources, which require neither optical connecters nor special care for polarization dependence. There are two types of integrations for on-chip light sources: monolithic integration with silicon or germanium lasers and hybrid integration with compound semiconductor lasers. Because the efficiency and output power of monolithically integrated Ge-on-Si lasers are still low for interchip interconnect applications [8], we have chosen hybridly integrated lasers. There are two types of compound semiconductor lasers for optical interconnects: edge emitting lasers and vertical cavity surface emitting lasers (VCSELs). Because VCSELs cannot maintain single mode operation when the optical output is high, we have chosen edge-emitting lasers. There are also two types of hybrid lasers in terms of optical coupling structures between the active waveguide and the silicon waveguide: evanescent-coupled lasers [9] and butt-coupled lasers [10]. The evanescent-coupled lasers have higher tolerance against alignment error when the compound semiconductor chips are mounted on the silicon substrate than the butt-coupled ones. However, we have found that the bandwidth density and power consumption per channel in laser diodes (LDs) can be improved by using a branching configuration, in which the light from a single LD is divided and distributed to many channels [11], and we think the efficiency and output optical power of the evanescent-coupled lasers are not high enough for the branching configuration. We have therefore chosen to use butt-coupled hybrid lasers for interchip interconnect applications and have developed spot-size converters (SSCs) between LDs and silicon optical waveguides to relax the alignment tolerance as will be mentioned later.

2.3 C. Conceptual Model

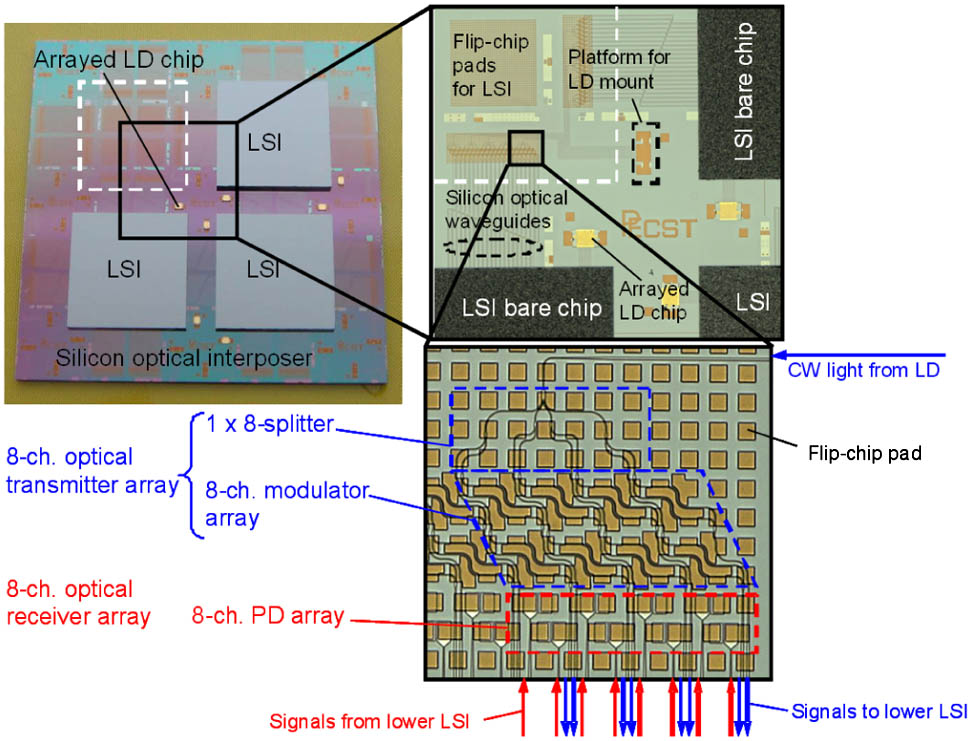

Based on the above examinations, we previously proposed a photonics–electronics convergence system for interchip interconnects [6,12]. A conceptual model of the system is shown in Fig.

Fig. 2. Conceptual model of photonics–electronics convergence system for interchip interconnects.

This system enables us to replace the conventional electronic wires on a printed circuit board (PCB) with the optical interconnects on a silicon substrate one hundredth the size of a PCB. This silicon optical interposer has wide bandwidth capabilities due to the properties of its optical signals. Since the silicon substrates can be fabricated using a CMOS-compatible process, they have quite high density and are low in cost. Furthermore, users do not have to worry about any optical issues (such as optical coupling, optical reflection, or polarization dependence) because this system is optically complete and closed without needing any optical inputs or outputs.

3. CONFIGURATION AND CHARACTERISTICS OF OPTICAL COMPONENTS

To demonstrate the feasibility of the photonics–electronics convergence system, we fabricated a high-density silicon optical interposer that mainly consisted of silicon optical waveguides, silicon optical modulators, germanium PDs, LDs, and SSCs. The configurations and characteristics of these optical components were investigated as follows.

3.2 A. Silicon Optical Waveguides

Generally, there are two types of silicon optical waveguides in terms of their core cross section shapes: rib-shaped and rectangular. The propagation loss of the rib-shaped waveguides is lower than that of the rectangular ones, but the rib-shaped waveguides pose difficulties in the fabrication process in that we have to stop etching the silicon layer to leave a precisely thin silicon slab. We think this issue is critical in terms of yields in mass production, especially (as will be explained later) for the yields of optical modulators. We have therefore chosen rectangular core waveguides for our silicon optical interposers and have developed fine processes for low-loss rectangular core waveguides. The developed processes mainly consist of multiple exposure technique in variable-shaped-beam (VSB) electron beam (EB) lithography and optimization of EB resist and etching processes. By applying these techniques, the field stitching error and line edge roughness (LER) were drastically reduced to 7.9 and 1.9 nm, respectively [13].

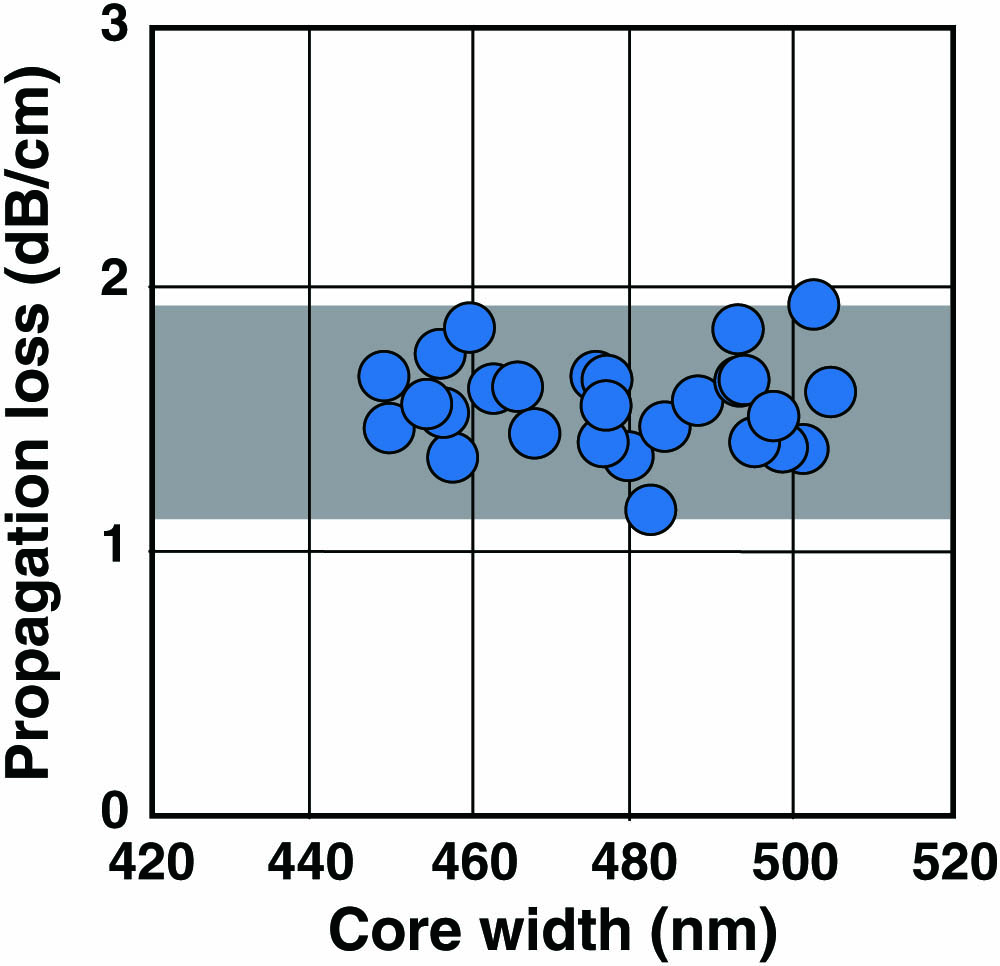

Figure

3.3 B. Silicon Optical Modulators

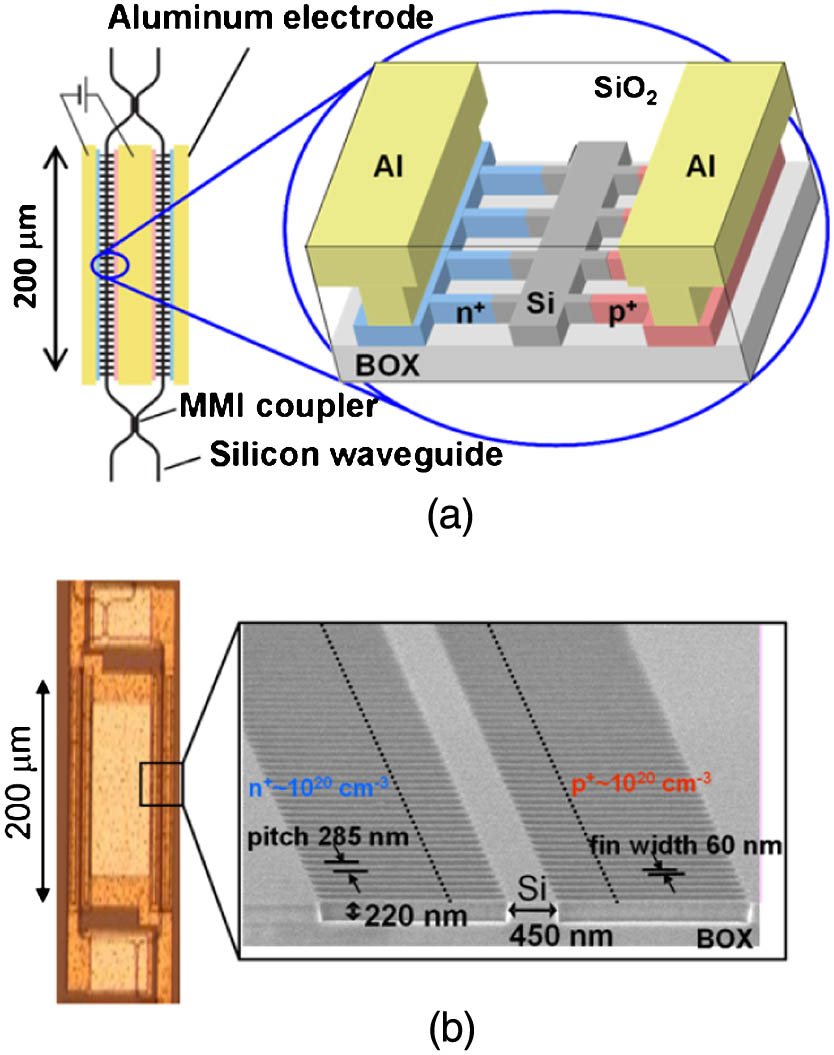

There has been a lot of research on silicon optical modulators using the carrier plasma effect in PIN or PN diodes, most of it focused on using a doped silicon slab in the rib-shaped waveguides to make electric contact between the waveguide core and metal electrodes [1416" target="_self" style="display: inline;">–

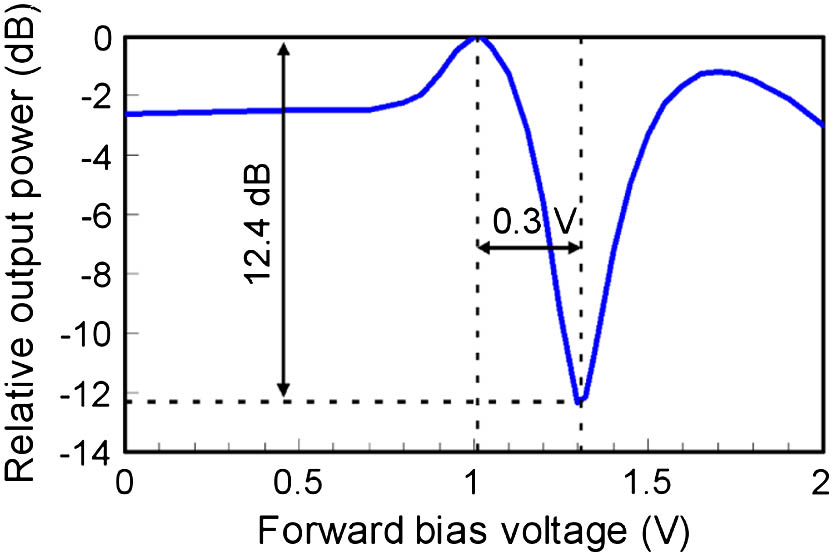

The measured DC response of the optical modulator is plotted in Fig.

3.4 C. Germanium Photodetectors

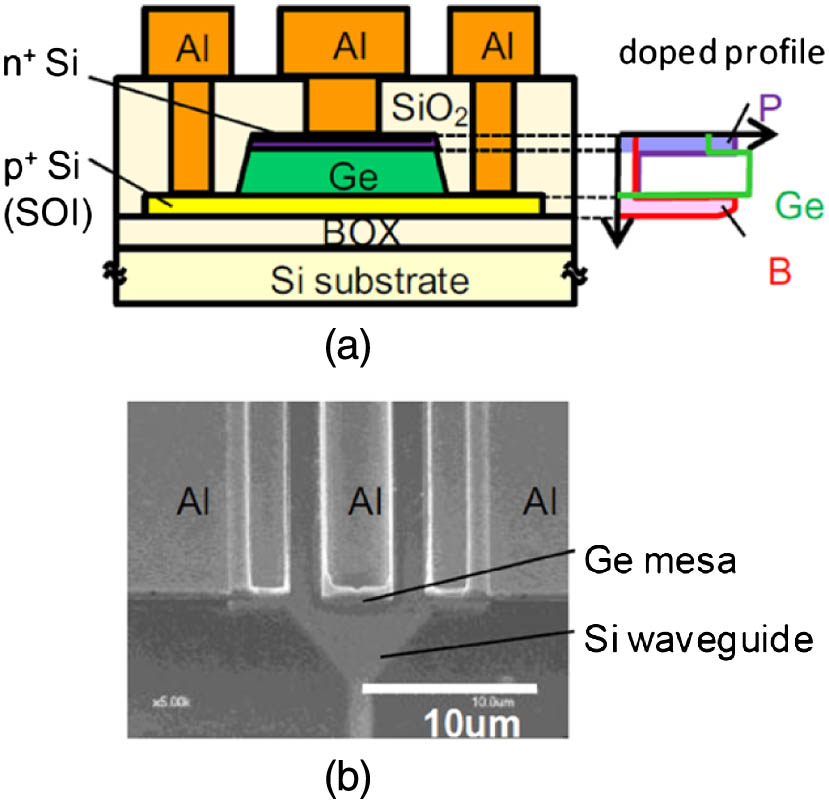

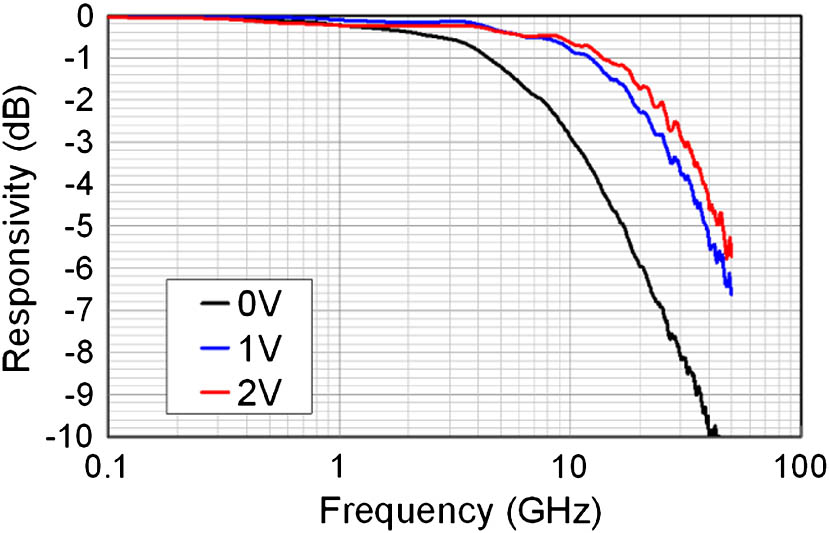

There are generally two types of germanium PDs that we can monolithically integrate on a silicon substrate: PIN-PDs and metal-semiconductor-metal (MSM) PDs. MSM-PDs require fewer fabrication steps but finer patterning and alignment than PIN-PDs. In this work we fabricated PIN-PDs for the silicon optical interposers [18]. Figure

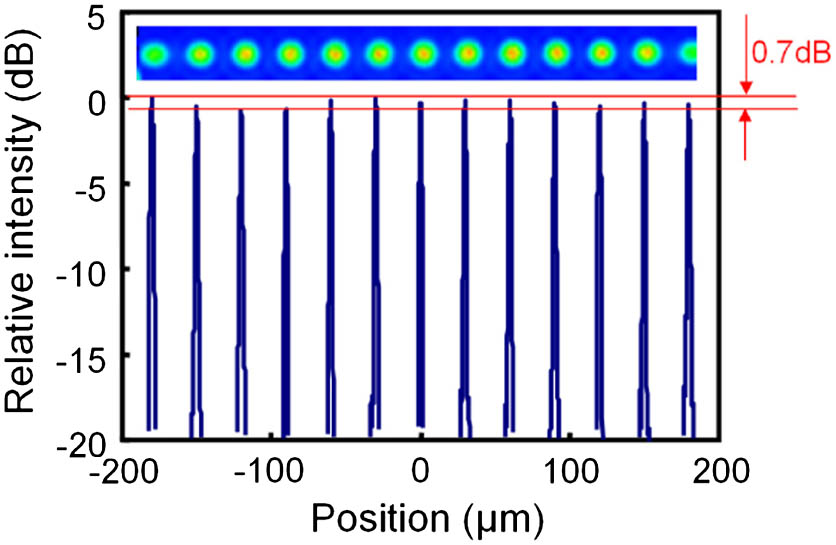

3.5 D. Arrayed Laser Diodes

Figure

3.6 E. Spot-Size Converters

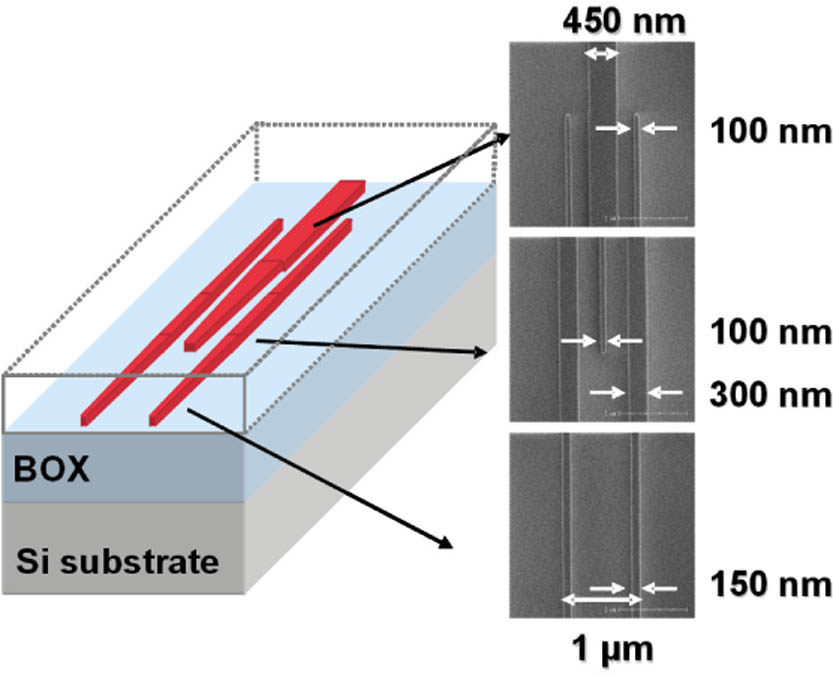

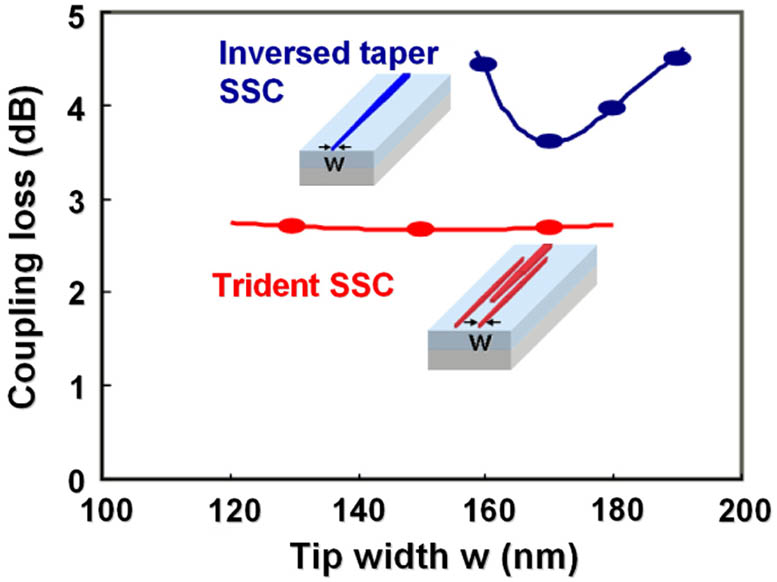

SSCs between the LDs and silicon optical waveguides are key components for the silicon optical interposers in terms of their optical power budget and fabrication process simplicity. We previously used three types of SSC: tapered silicon waveguide; inversed taper silicon waveguide; and SiON waveguide. Although the first two did not need additional processes, the first had a large coupling loss [6] and the second had a very small process margin, as will be shown later. The third type had a low coupling loss but needed additional processes [10]. We subsequently introduced a SSC called a trident [20], the schematic structure and SEM images of which are shown in Fig.

Figure

Fig. 11. Coupling losses of the trident SSC and an inversed taper SSC with various silicon core tip widths.

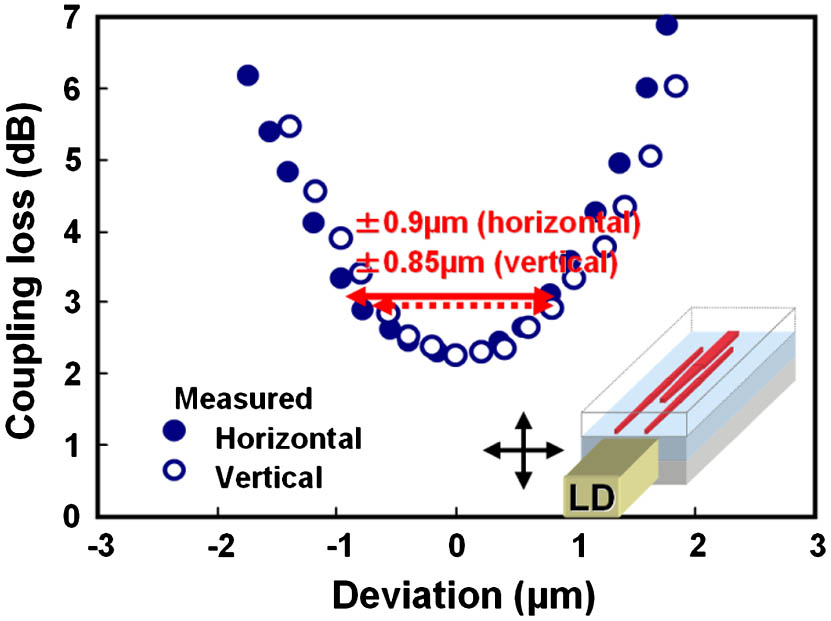

Measured coupling losses between the LD and the trident SSC with various alignment deviations in the horizontal and vertical directions are plotted in Fig.

Fig. 12. Coupling losses between the LD and the trident SSC with various alignment deviations in the horizontal and vertical directions.

4. DESIGN AND FABRICATION OF SILICON OPTICAL INTERPOSERS

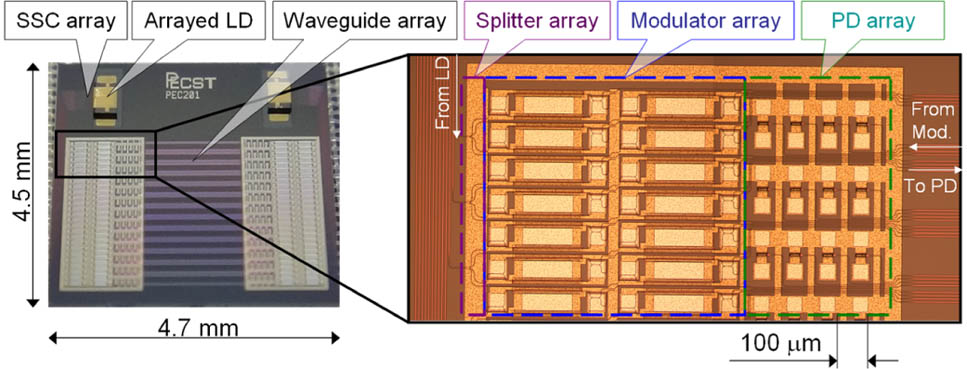

As mentioned earlier, LSI bare chips are supposed to be mounted on the interposer using flip-chip bonding. ITRS projections have indicated that the pitches of flip-chip pad arrays should stop shrinking at around 100 μm [2]. Therefore, we designed our silicon optical interposers so that the pad pitches of our optical modulators and PDs were 100 μm. We used

The silicon optical interposers were fabricated from 4 in. (100 mm) silicon-on-insulator (SOI) wafers in the Super Clean Room at AIST Tsukuba West by CMOS process technology. The thicknesses of the buried oxide layer and the SOI layer were 3 μm and 220 nm, respectively. The silicon optical waveguide cores, as well as trident SSCs,

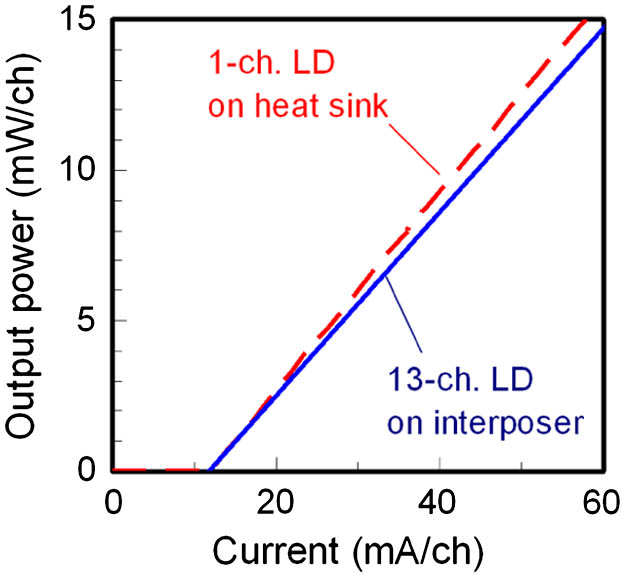

The I-L characteristics of the LDs measured without temperature control are plotted in Fig.

A photograph of one of our fabricated silicon optical interposers is shown in Fig.

5. DATA LINK EXPERIMENTS USING SILICON OPTICAL INTERPOSERS

We performed data link experiments as follows. All 13 channels of the arrayed LD were simultaneously driven by a single DC current. The CW light from the LD was a wavelength of 1530 nm and a TE-like mode. It was coupled to the silicon optical waveguide by the trident SSC and then divided into four by the

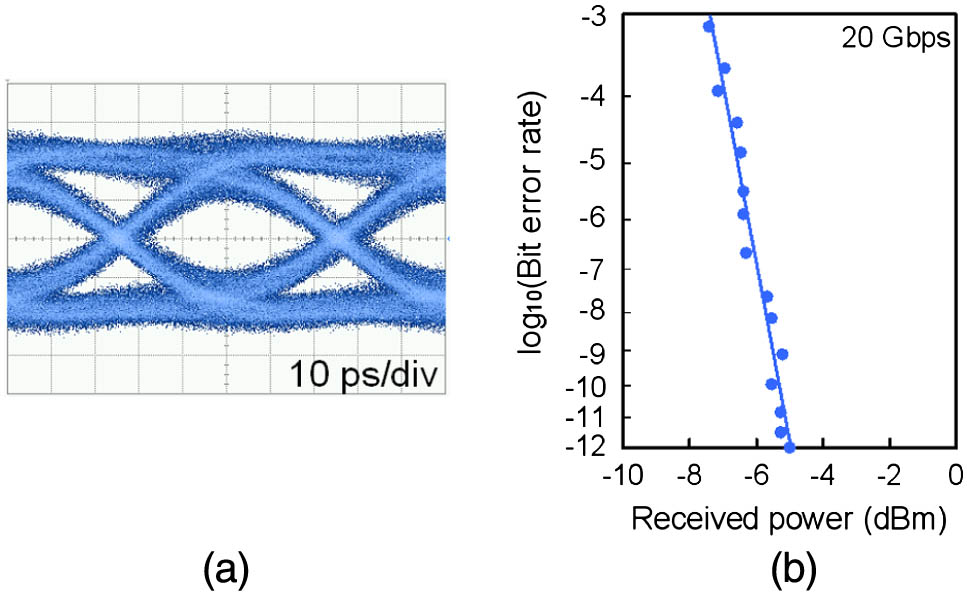

The measured eye diagram of the PD output at 20-Gbps NRZ with a

The footprints of the optical components per link channel are listed in Table

Table 1. Per-Channel Footprints of Optical Components.

|

Since this system is optically complete and closed and no temperature sensitive components are used, we did not need to align the fibers, control the polarization, or control the temperature throughout the experiments.

6. CONCLUSIONS

We developed a photonics–electronics convergence system with a silicon optical interposer in order to solve the bandwidth bottleneck problem facing interchip interconnects. We examined integration between photonics and electronics and integration between light sources and silicon substrates and then fabricated a conceptual model of the proposed system based on the results of these examinations. We also investigated the configurations and characteristics of the optical components of the silicon optical interposer, including silicon optical waveguides, silicon optical modulators, germanium PDs, arrayed LDs, and SSCs. We then demonstrated the feasibility of the system with a high-density optical interposer fabricated by using silicon photonics integrated with these optical components on a single silicon substrate. Using this silicon optical interposer enabled us to achieve error-free data links at a 20-Gbps line rate and a high bandwidth density of

For practical applications, the interposers should be usable under high temperature conditions so that they can cope with the heat generated by the mounted LSIs. Since the LSI bare chips are mounted near the LDs, the LDs are expected to suffer from the heat. To overcome the heat problem, we are also developing temperature insensitive light source with quantum dot lasers for the system [21]. We plan to demonstrate silicon optical interposers with quantum dot lasers in the near future.

Although we used 4 in. (100 mm) wafers and EB lithography for fabricating the prototypes of the interposers in this work, we are also developing fabrication processes and devices using 300 mm wafers and ArF immersion lithography for future mass production and higher performance [2224" target="_self" style="display: inline;">–

[2]

[19] N. Fujioka, T. Chu, M. Ishizaka. Compact and low power consumption hybrid integrated wavelength tunable laser module using silicon waveguide resonators. J. Lightwave Technol., 2010, 28: 3115-3120.

Article Outline

Yutaka Urino, Tatsuya Usuki, Junichi Fujikata, Masashige Ishizaka, Koji Yamada, Tsuyoshi Horikawa, Takahiro Nakamura, Yasuhiko Arakawa. High-density and wide-bandwidth optical interconnects with silicon optical interposers [Invited][J]. Photonics Research, 2014, 2(3): 030000A1.