基于CMOS的高响应度太赫兹探测器线阵【增强内容出版】

1 引言

太赫兹(Terahertz,简称THz)波为频率介于0.1~10 THz的电磁波,直至19世纪末才被正式命名。其在频谱上位于微波与红外线两大电磁波之间,兼具两者的性能,具有重大研究意义和广泛应用前景。太赫兹技术被众多国家的高校以及科研机构深入探索,美国甚至将太赫兹技术评为“改变未来世界的十大技术”之一[1],随着研究的不断深入,制约太赫兹技术发展的瓶颈相继被攻克。目前,太赫兹波凭借其高带宽、低光子能量以及对非金属、非极性材料的高穿透性等优势在高速通信、生物医疗、无损检测和安全检查等领域有广泛的应用[2][3]。太赫兹探测器作为应用领域的关键器件,自探测的机理被报道以来,其高精度的成像应用成为研究热点[4][5]。

1996年,M. Dyakonov和M. Shur论证了半导体场效应晶体管对远超出自身截止频率的太赫兹等离子体波的探测机制[6],为利用场效应管实现太赫兹功率探测奠定理论基础,并提出切实可行的实践方法,使基于CMOS工艺的混频探测迅速发展。采用单像素探测电路结构以及阵列探测电路结构的成功案例相继被报道。文献[7]设计的自混频单像素探测器,在0.595 THz处响应度为0.35 kV/W,噪声等效功率为42 pW/Hz1/2。而文献[8]中则通过降低场效应管栅极与源极间寄生电容的方式提高探测器的响应度,在0.65 THz辐射下响应度提高到5.5 kV/W,噪声等效功率低至9.1 pW/Hz1/2。采用高响应度的单像素阵列布局设计将更有利于实现高精度的透射成像。文献[9]将单像素电路排列成3 × 5的探测器阵列,集成片上电压放大器后,响应度高达80 kV/W,噪声等效功率为300 pW/Hz1/2,可在0.65 THz信号透射下实现对信封内的金属物体高精度成像。中国科学院半导体研究院吴南健教授团队也在文献[10]中提出了工作在0.86 THz的3 × 5的探测器阵列,该探测系统具有106 pW/Hz1/2的噪声等效功率,3.3 kV/W的响应度,可以实现对绿叶等非金属材料的高精度成像。

基于以上分析,本文将太赫兹自混频功率探测电路、片上电压放大电路和片上天线相结合,采用电磁场与电路联合仿真方法,在不改变制造工艺情况下,通过标准CMOS工艺完成太赫兹线阵的设计。经过设计、仿真、优化及流片,实现了1 × 3探测器线阵。本文第一小节介绍了探测器的基本原理和设计考虑,第二小节详尽描述了具体的探测器线阵设计过程,第三节介绍了探测器线阵响应度、噪声等效功率等测量结果。

1 太赫兹探测器基本原理和设计考虑

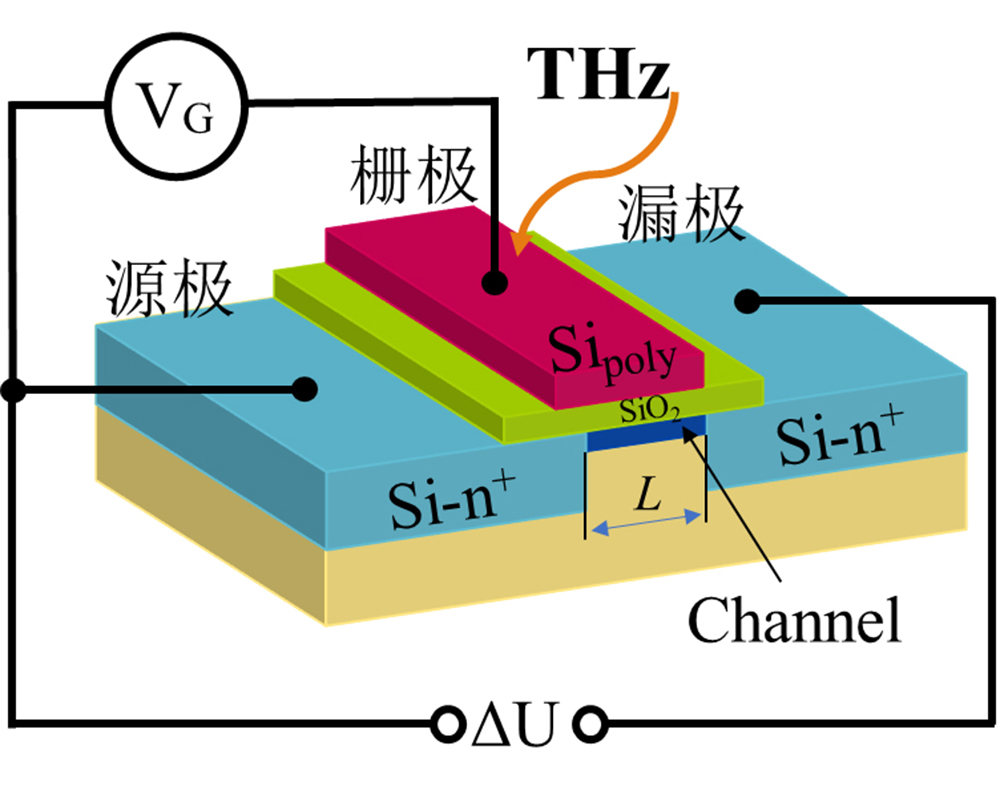

M. Dyakonov和M. Shur提出场效应管借助二维电子气沟道的分布效应,能够实现对超出晶体管自身截止频率的太赫兹波信号进行有效平方率检波,输出与输入功率成比例的响应电流或电压。可利用非准静态模型对太赫兹信号在场效应晶体管中的作用原理进行分析,如

电压响应度为响应电压与太赫兹输入功率的比值,则根据

其中Rin表示太赫兹输入端口阻抗的实部。虽然此公式由MOSFET工作在饱和区的公式推导而出,但是从

其中SV表示噪声功率谱密度,在太赫兹功率探测电路中噪声主要来源于热噪声和闪烁噪声。闪烁噪声与频率成反比,在太赫兹频段可忽略不计,则沟道热噪声成为噪声的主要来源,其噪声功率谱密度为

kB为玻尔兹曼常数,T为开尔文温度,γ是由工艺决定的常数,ro为MOSFET沟道电阻。将

同样由表达式可知,当MOSFET工作在亚阈值状态下时可取得最小的噪声等效功率。

图 2. 自混频功率探测器电路结构(a)源极驱动;(b)栅极驱动;(c)源极差分驱动

Fig. 2. The structure of self-mixing power detector circuit(a)source driven;(b)gate driven;(c)differential source driven

目前,最受追捧的三种自混频功率探测电路结构主要包括:源极驱动电路[10](a),栅极驱动电路[11][12](b)和源极差分驱动电路[13][14](c)。电路(b)原理图中的栅极驱动省略了栅极的偏置电压。其中,源极驱动电路和栅极驱动电路都是从MOSFET的单端输入,在沟道内发生自混频后在漏极输出混频信号。而源极差分驱动电路则在两个MOSFET的源极输入差分信号,漏极作为交流地,不仅可以保证晶体管的差分特性,而且能够传递电路的混频信号。此外,源极差分驱动结构可避免大的栅极与源极间寄生电容和负载阻抗的影响[15]。其良好的宽带性基本只依赖于天线信号耦合的效率以及天线与探测电路之间的阻抗匹配。三种电路结构的响应度仿真对比如

图 3. 三种自混频探测电路结构的响应度仿真对比

Fig. 3. Response simulation comparison of three kinds of self-mixing detection circuit

2 探测器阵列实现

2.1 电路整体结构

探测器阵列由3个太赫兹像素线性排列,每个像素由带交叉耦合电容的源极差分驱动自混频功率探测电路、高增益片上环形差分天线和集成电压放大器组成。各像素单元的输出相互独立,阵列规模的设计提高探测器中的像素点个数,实现高效率和高精度成像。3个太赫兹像素以80 μm的间距等间隔排列成行,共享同一栅极偏置电压和电源电压。像素之间通过地平面隔离减少像素之间天线的相互耦合。此外,差分环形天线的轴心位置需要进行接地处理,为差分MOSFET提供直流回路。

2.2 片上天线设计

片上天线是探测器中的关键模块,需要高增益的天线接收微弱的太赫兹辐射信号[16]。

图 5. 0.18 μm CMOS 工艺物理结构和天线模型

Fig. 5. Physical structure and antenna model of 0.18 μm CMOS process

2.3 电路设计

本文采用的探测器像素单元电路如

图 9. 自混频功率探测电路的输入阻抗仿真结果

Fig. 9. The input impedance simulation results of self-mixing power detector

当栅极偏置在0.41 V时,在没有片上放大器的情况下,在目标频点0.3 THz处获得的最大响应度为550 V/W,最小噪声等效功率为9.8 pW/Hz1/2,仿真结果如

图 10. 探测电路响应度与噪声等效功率仿真结果

Fig. 10. Simulation results of detector responsiveness and equivalent noise power

集成电压放大器对自混频探测电路的输出信号进行放大处理,提高探测系统的响应度,增强系统的驱动能力。低噪声、高输入阻抗是集成电压放大器要具备的性能,因为自混频功率探测电路的输出是微弱的直流信号,低噪声和高输入阻抗才能保证精确捕获输出的电压响应信号。本文采用如

图 11. 集成电压放大器的性能仿真结果

Fig. 11. Performance simulation results of integrated voltage amplifier

3 实验测试结果

首先将探测器芯片绑定到芯片外围扩展电路板上,然后利用斩波-锁相技术测量探测器阵列。由太赫兹信号源、斩波器、锁相放大器和计算机搭建如

图 14. 测试平台的搭建(a)测试系统的框图;(b)测试平台的实际环境

Fig. 14. Test platform construction (a) block diagram of the test system; (b) The actual environment of the test platform

对于静态测试,首先将太赫兹信号源频率和功率进行固定,使其保持聚焦状态。固定太赫兹信号源与探测器的相对物理位置后,关闭太赫兹信号源的电源,给探测器阵列芯片上电,在锁相放大器上可观察到0.18 V左右的电压输出。此现象可能为芯片内部或PCB板级电路导致的输出直流偏移。为了继续验证探测器是否存在响应,打开太赫兹信号源,为探测器提供信号辐射,锁相放大器的输出电压会增加,表明探测器是有响应的。后续的实验测量和测量结果均以输出电压的相对值作为探测器的响应输出。将探测器栅极偏压引脚连接到直流电压源,从0.1 V到1 V,以0.05 V为步进进行调整,观察锁相放大器的测试结果并进行记录。记录的实验数据经过计算表示为响应度描绘在

表 1. 性能总结对比

Table 1. Performance summary and comparison

|

图 17. 噪声等效功率的仿真与测试结果

Fig. 17. Simulation and measurement results of noise equivalent power

对于出现不一致,以及响应度降低原因分析认为,可能是受到测试环境和芯片本身的限制,测试过程中会有信号损失以及干扰带来的测试误差。其中误差来源包括但不限于1)无法准确识别探测器接收的太赫兹功率,2)测量系统中驻波引起的响应度测量与距离和频率的纹波,3)阵列中各像素点周围环境的不一致,以及4)由于有限地平面尺寸引起的天线纹波。这些因素的叠加可以对测量的响应度和NEP贡献高达2 dB的误差[20]。受限于实验的测试环境和实验设备,具体的误差无法补偿,所以测试结果的计算中太赫兹入射功率的值均以衰减3 dB为实际上太赫兹接收到的功率。

对于动态测试,保证测试平台维持电压响应度的测试配置,在太赫兹信号源和太赫兹探测器之间加入隔挡物,例如金属薄板、A4纸等,观察输出电压的变化。动态实验选用响应度最大的端口2进行测试,且选择自混频功率探测电路的直接输出端口,未经过像素单元中的片上放大器,在上位机中可观察到电压信号波动的图像。如

图 18. 锁相放大器显示的太赫兹探测响应波形

Fig. 18. Terahertz detection waveform displayed by a phase-locked amplifier

通过更换不同的隔挡物,可发现探测器对不同隔挡物的响应程度不同。

图 19. 对不同隔挡物(A4纸和铜板)的透射结果

Fig. 19. Transmission results for different barriers(A4 paper and copper sheet)

4 结论

本文采用0.18 μm CMOS工艺完成高响应度探测器线阵的制备。通过分析对比了几种常用的自混频功率探测结构的性能,选择源极差分驱动结构作为自混频功率探测结构,改进后的带交叉耦合电容的结构增强太赫兹信号在小尺寸晶体管沟道内的强度,提高晶体管漏极和源极间的输出电压,从而提高探测器的响应度。通过结合电磁仿真与电路仿真,完成高增益片上环形差分天线、源极差分驱动自混频功率探测电路和集成低噪声电压放大器的联合仿真,优化模块间的级联使探测器系统整体性能达到最优。不修改制造工艺情况下,在0.5 mm × 1 mm的面积上实现1 × 3线阵的制备,其中包括焊盘和片上天线。在室温条件下搭建测试平台对探测器阵列芯片进行测试,当栅极偏置电压为0.42 V,晶体管工作在亚阈值区,此时该探测器的最大响应度可达43.8 kV/W,最小NEP为20.5 pW/Hz1/2。探测器阵列芯片的动态测试表明该探测器阵列可区分不同材质的物体。实验测试表明本文提出的探测器可进一步应用到太赫兹探测成像系统中,待完善探测器响应信号数据处理电路和成像算法后,可实现太赫兹探测成像。值得注意的是,采用的多像素探测方法在于提高检测速度,但由于缺少通道间的相位信息,相较于包含响应相位信息的外差混频探测方式,其灵敏度主要依赖于单个天线单元的增益,响应信号中也只包含幅值信息。

[1] 张玉平, 唐利斌, 刘玉菲, 等. 太赫兹新型探测器的研究进展及应用[J]. 红外与毫米波学报, 2020, 39(2): 191-210.

[2] 周智伟. 太赫兹技术发展综述(上)[J]. 军民两用技术与产品, 2020, 435(1): 40-44.

ZHOU Zhi-Wei. Review of terahertz technology development (Part I)[J]. Dual Use Technologies & Products, 2020, 435(1): 40-44.

[3] 杨静, 邱杰夫, 姜辉, 等. 太赫兹技术在绘画类文物上的应用与展望[J]. 红外与毫米波学报, 2022, 41(01): 218-229.

YANG Jing, QIU Jie-Fu, JIANG Hui, et al. The application of terahertz technology in paintings[J]. Journal of Infrared and Millimeter Waves, 2022, 41(01): 218-229.

[4] Hillger, Philipp, Grzyb, et al. Terahertz imaging and sensing applications with silicon-based technologies[J]. IEEE Transactions on Terahertz Science and Technology, 2019, 9(1): 1-19.

[5] 刘宏翔, 姚建铨, 王与烨, 等. 太赫兹波近场成像综述[J]. 红外与毫米波学报, 2016, 35(03): 300-309+376.

LIU Hong-Xiang, YAO Jian-Quan, WANG Yu-Ye, et al. Review of THz near-field imaging[J]. Journal of Infrared and Millimeter Waves, 2016, 35(03): 300-309+376.

[6] Dyakonov M, Detection Shur M.. mixing, and frequency multiplication of terahertz radiation by two-dimensional electronic fluid[J]. IEEE Transactions on Electron Devices, 1996, 43(3): 380-387.

[7] Boppel S, Lisauskas A, Mundt M, et al. CMOS integrated antenna-coupled field-effect transistors for the detection of radiation from 0.2 to 4.3 THz[J]. IEEE Transactions on Microwave Theory and Techniques, 2012, 60(12): 3834-3843.

[8] Yang Qi-Xuan, Ji Xiao-Li, Xu Yue, et al. Improved performance of CMOS terahertz detectors by reducing MOSFET Parasitic Capacitance[J]. IEEE Access, 2019, 7: 9783-9789.

[9] Ojefors E, Pfeiffer U R, Lisauskas A, et al. A 0.65 THz focal-plane array in a quarter-micron CMOS process technology[J]. IEEE Journal of Solid-State Circuits, 2009, 44(7): 1968-1976.

[10] Liu Zhao-Yang, Liu Li-Yuan, Yang Jie, et al. A CMOS fully integrated 860-GHz terahertz sensor[J]. IEEE Transactions on Terahertz Science & Technology, 2017, 7(4): 455-465.

[11] Moustafa K, Matteo P. Response Optimization of antenna-coupled FET detectors for 0.85-to-1-THz imaging[J]. IEEE Microwave & Wireless Components Letters, 2018, 28(10): 903-905.

[12] Schuster F, Coquillat D, Videlier H, et al. Broadband terahertz imaging with highly sensitive silicon CMOS detectors[J]. Opt. Express, 2011, 19(8): 7827-7832.

[13] Al, Hadi, Richard, et al. A 1 k-pixel video camera for 0.7–1.1 terahertz imaging applications in 65-nm CMOS[J]. IEEE Journal of Solid-State Circuits, 2012, 47(12): 2999-3012.

[14] Al, Hadi, Richard, et al. A terahertz detector array in a SiGe HBT technology[J]. IEEE Journal of Solid-State Circuits, 2013, 48(9): 2002-2010.

[15] Ferrerasmayo M, Cibiraite-Lukenskiene D, Lisauskas A, et al. Broadband sensing around 1 THz via a novel biquad-antenna-coupled low-NEP detector in CMOS[J]. IEEE Transactions on Terahertz Science and Technology, 2020, 11(1): 16-27.

[16] He Ye-Jun, Chen Ya-Ling, Zhang Long, et al. An overview of terahertz antennas[J]. China Communications, 2020, 17(7): 124-165.

[17] Shaulov E, Jameson S, Socher E. A zero bias J-band antenna-coupled detector in 65-nm CMOS[J]. IEEE Transactions on Terahertz Science and Technology, 2021, 11(1): 62-69.

[18] Xu Lei-Jun, Guan Jia-Ning, Bai Xue, et al. A novel CMOS multi-band THz detector with embedded ring antenna[J]. Journal of Infrared and Millimeter Waves, 2017, 38(10): 1189-1205.

[19] Kim D Y, Park S, Han R, et al. Design and demonstration of 820-GHz array using diode-connected NMOS transistors in 130-nm CMOS for active imaging[J]. IEEE Transactions on Terahertz Science and Technology, 2016, 6(2): 306-317.

[20] Uzunkol M, Gurbuz O D, Golcuk F, et al. A 0.32 THz SiGe 4 x 4 imaging array using high-efficiency on-chip antennas[J]. IEEE Journal of Solid-State Circuits, 2013, 48(9): 2056-2066.

[21] Pleterek A, Trontelj Janez. A self-mixing NMOS channel-detector optimized for mm-wave and THZ signals[J]. Journal of Infrared and Millimeter Waves, 2012, 33(6): 615-626.

[22] UzunkolM, EdwardsJ M, RebeizG M. A 0.3 THz 4 × 4 cold-FET imaging array in 45 nm CMOS SOI[C] USA: Microwave Symposium. IEEE, 2014:1-4.

[23] Yoon D, Kim J, Yun J, et al. 300-GHz direct and heterodyne active imagers based on 0.13-μm SiGe HBT technology[J]. IEEE Transactions on Terahertz Science and Technology, 2017, 7(5): 536-545.

白雪, 张子宇, 徐雷钧, 赵心可, 范小龙. 基于CMOS的高响应度太赫兹探测器线阵[J]. 红外与毫米波学报, 2024, 43(1): 70. Xue BAI, Zi-Yu ZHANG, Lei-Jun XU, Xin-Ke ZHAO, Xiao-Long FAN. High responsivity Terahertz detector linear array based on CMOS[J]. Journal of Infrared and Millimeter Waves, 2024, 43(1): 70.