Digital-analog hybrid optical phase-lock loop for optical quadrature phase-shift keying  Download: 933次

Download: 933次

For the digital coherent optical communication system, the receiver samples the analog electrical signals through a high-speed analog-to-digital converter (ADC). In general, the bandwidth of the electrical signal is equal to the baud rate. According to the Nyquist sampling theorem, the sampling rate of the ADC is twice the baud rate. The digital signal processor recovers the digital baseband signal based on the frequency offset estimation algorithm and carrier phase recovery algorithm[1]. With the increasing of the communication rate, the sampling rate of the ADC and the digital signal processor are challenged[2]. At the same time, the power consumption of the receiver will increase[3].

The homodyne coherent receiver based on optical phase-lock loop (OPLL) has attracted attention due to its low power consumption. The losses caused by the receiver can be compensated by an erbium-doped fiber amplifier (EDFA)[4]. Compared with binary phase-shift keying (BPSK), the quadrature phase-shift keying (QPSK) can carry 2 bits of information per symbol[5]. In 2002, Griffin et al. studied the optical differential QPSK (oDQPSK). The signal is demodulated by using an optical delay-and-add structure and is easier to realize than a homodyne coherent receiver[6]. However, the differential demodulation scheme suffers from a sensitivity penalty of about 2.3 dB compared with the ideal sensitivity of coherent QPSK detection[7]. In 2006, Pfau et al. reported the real-time synchronous QPSK transmission and digital in-phase quadrature (IQ) receiver. A 400 Mbaud QPSK data was transmitted quasi-error-free in a self-homodyne configuraton[8]. For an ideal shot-noise limited optical QPSK homodyne/heterodyne detection, the quantum limit of sensitivity for a bit error rate (BER) is 36 photons persymbol (18 photons/bit) and has an intrinsic 3 dB penalty compared with homodyne BPSK detection, equaling the sensitivity of heterodyne BPSK detection[9].

For the multi-gigabit QPSK receiver based on OPLL, it is difficult to extract the phase-error signal and the coefficient setting of the OPLL[10]. In 1992, Norimatsu et al. adopted the decision-directed phase-lock loop (PLL), and the phase-error signal was extracted by using digital exclusive OR (EX-OR) circuits instead of analog circuits[11]. But, this OPLL scheme generates the four-fold phase error and offers 90° phase ambiguity, which needs to be eliminated by differential encoding. In 2014, Fujii et al. reported QPSK demodulation based on digital OPLL[12]. The phase-error signal was extracted by a track and hold (T&H) circuit and a field-programmable gate array (FPGA). A second-order active loop filter was used and had a better phase margin. However, compared with the first-order active loop filter, the complexity of the coefficient setting is greatly increased.

In this Letter, the fourth-power phase-lock algorithm based on an FPGA is presented. The first-order active filter is used as a loop filter. This scheme is applicable to M-array phase-shift keying (PSK) and quadrature amplitude modulation (QAM) signals by changing the relevant digital processing algorithm. The performance of a QPSK homodyne coherent receiver is examined. The Padé approximation is adopted in calculation of the phase-error variance with the non-negligible loop propagation delay, and the loop natural frequency is optimized.

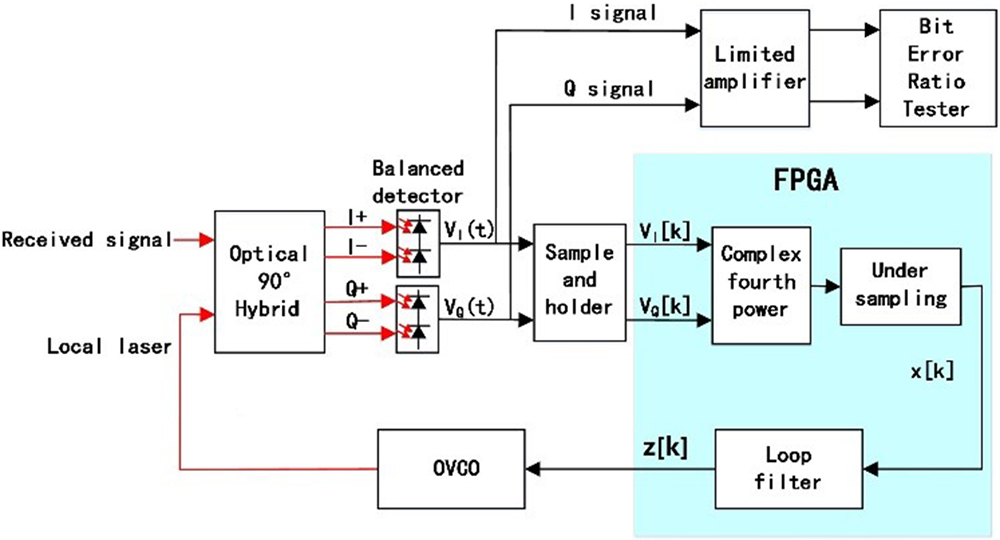

First of all, Fig.

and , the two analog signals, are sampled and quantized synchronously by an ADC with a sampling rate of 125 MHz. In order to remove the modulated signal and recover the phase-error signal, the digitalized signals are input into the normalized complex fourth-power look-up table implemented in FPGA. The function of the normalized complex fourth-power look-up table follows represents the imaginary part of the normalized complex signal. According to Eqs. (

To simplify the analysis, we assume that the loop remains in lock with a small phase error,

Equation (

We investigate the functionality of an optical voltage controlled oscillator (OVCO). As shown in Fig.

Next, we introduce the linear model diagram of an analog optical QPSK fourth-power PLL, as shown in Fig.

According to Fig.

The single sided power spectral densities (PSDs) of the phase noise caused from and of the shot noise caused from are expressed as represents the total linewidth of the signal laser and local laser; is the coefficient of the noise; is the electron charge. In the condition that the phase noise and shot-noise processes are independent from each other, the variance of the steady-state phase error has already been obtained as

In order to get the analytic solution, one method is using the Padé approximation[14]. The (2,2)th Padé approximation of is given by

According to the (2,2)th Padé approximation with the damping factor, is set to be 0.707, and Eq. (

Now, we optimize the loop parameters. Table

Table 1. Experimental Parameters

|

The optimized natural frequency under specific loop delay is shown in Fig.

The increase of the loop delay will reduce the natural frequency . In order to reduce the effect of loop delay , the LPCA is used. The principle of LPCA is to average the signal eight times and then input the averaged signal to the interface of the DDS’s phase control word. It will generate the corresponding phase compensation.

According to the above analysis, the variance of the steady-state phase error is related to the linewidth of the laser. In general, the single sided PSD of frequency fluctuation can be tested by the instrument. can be expressed as

Figure

Fig. 6. (a) Frequency fluctuation PSD of the transmitter (TX)/receiver (RX) laser and (b) the constellation of the QPSK modulation signal.

We built a QPSK homodyne coherent receiver based on the fourth-power OPLL. The performance of the OPLL is verified by simulation and experiment. In our experiment, the detector model is KPDX10G. The ADC model is EV10AQ190A. The series of the FPGA used in the experiments is xc7k420tffg901-2. ADC sampling delay is 69 ns; FPGA algorithm computing delay is 112 ns; digital-to-analog converter (DAC) delay (restricted by the hardware) is 338 ns, and the fiber delay is about 6 ns. The total loop delay is 525 ns. According to Eq. (

Table 2. Specification List about FPGA

|

In order to understand the signal form of each step in the OPLL algorithm, Fig.

Fig. 7. QPSK fourth-power phase-lock loop simulation: (a) the Lissajous of the original signal sampled by 125 MSa/s; (b) the fourth power of the original signal; (c) phase error of the phase-locked state; (d) the constellation of the recovered IQ signal.

We further analyze the sensitivity of the QPSK homodyne coherent receiver system, where the BER is affected by the signal-to-noise ratio (SNR) and phase-error variance. The probability of bit error is obtained by Rhodes as[16] is the bit rate. The is a Gaussian error function defined as

Prabhu has presented the sensitivity loss caused by phase-locked error. For a QPSK homodyne coherent detection, standard deviations of and correspond to power penalties of 0.5 dB and 1 dB at BER, respectively[17].

We measured the back-to-back BER of the QPSK communication receiver. Figure

In summary, a homodyne coherent optical receiver for demodulating 2.5 Gbaud/5 Gbaud QPSK has been studied. By means of digital-analog hybrid PLL, the requirements of bandwidth of PLL electronics and sampling rate are reduced. The phase-error signal is extracted by a fourth-power PLL. Through simulation and experiments, we have optimized the loop natural frequency under the non-negligible loop propagation delay. The receiving sensitivity reaches at bit rate of 2.5 Gbaud/5 Gbaud. By the LPCA, the accuracy of phase lock and stability of the receiver are improved, which is of great significance for the realization of higher-speed, high-sensitivity coherent optical communication systems. Improved results can be easily obtained by reducing the total loop delay and optimizing the performance of the detector. They would relax the requirement for laser linewidth and reduce the steady-state phase error of the PLL.

[1]

[2]

[3]

[4]

[5]

[6]

[7]

[9]

[11]

[12]

[13]

[14]

[15]

[16]

[17]

Shaowen Lu, Yu Zhou, Funan Zhu, Jianfeng Sun, Yan Yang, Ren Zhu, Shengnan Hu, Xiaoxi Zhang, Xiaolei Zhu, Xia Hou, Weibiao Chen. Digital-analog hybrid optical phase-lock loop for optical quadrature phase-shift keying[J]. Chinese Optics Letters, 2020, 18(9): 090602.