基于变形目镜和OLED的全景周视成像与显示技术  下载: 603次

下载: 603次

1 引 言

视频图像显示是光电图像信息获取过程的重要环节[1-3]。随着视频成像技术的发展,对于成像视场的要求也越来越高。目前周视的实现方式主要分为单视系统和多视系统两类:单视系统的代表主要是鱼眼成像系统、全景环形透镜成像系统和折反射透镜成像系统等;多视系统则以多摄像头成像为主要代表。其中单视系统难以兼顾视场和分辨率,而多视系统需要解决拼接缝隙的问题[4-5]。传统的光电成像系统的视场以及分辨率难以满足特定的需求,在增大视场与提高分辨率之间存在矛盾,无法同时满足大视场与高分辨率的要求。近年来,车载、舰载等运动载体或单兵警戒值守等诸多空间狭窄、视野受限场合对全景成像显示需求日趋迫切,虽然采用传统的凝视全景成像系统可解决全景成像问题,但在路面起伏较大的运动平台上,显示屏很难与人眼之间保持相对平稳,易造成观察者视觉疲劳甚至出现眩晕、恶心等不适。因此,新型全天候全景或周视高分辨成像与显示技术成为重要的发展方向。

本文提出一种基于变形目镜的全景/周视成像方案,在实现全景成像的同时具有较高的分辨率,解决了二者之间的矛盾。在此基础上,研制并验证实验系统。

2 系统概述与设计

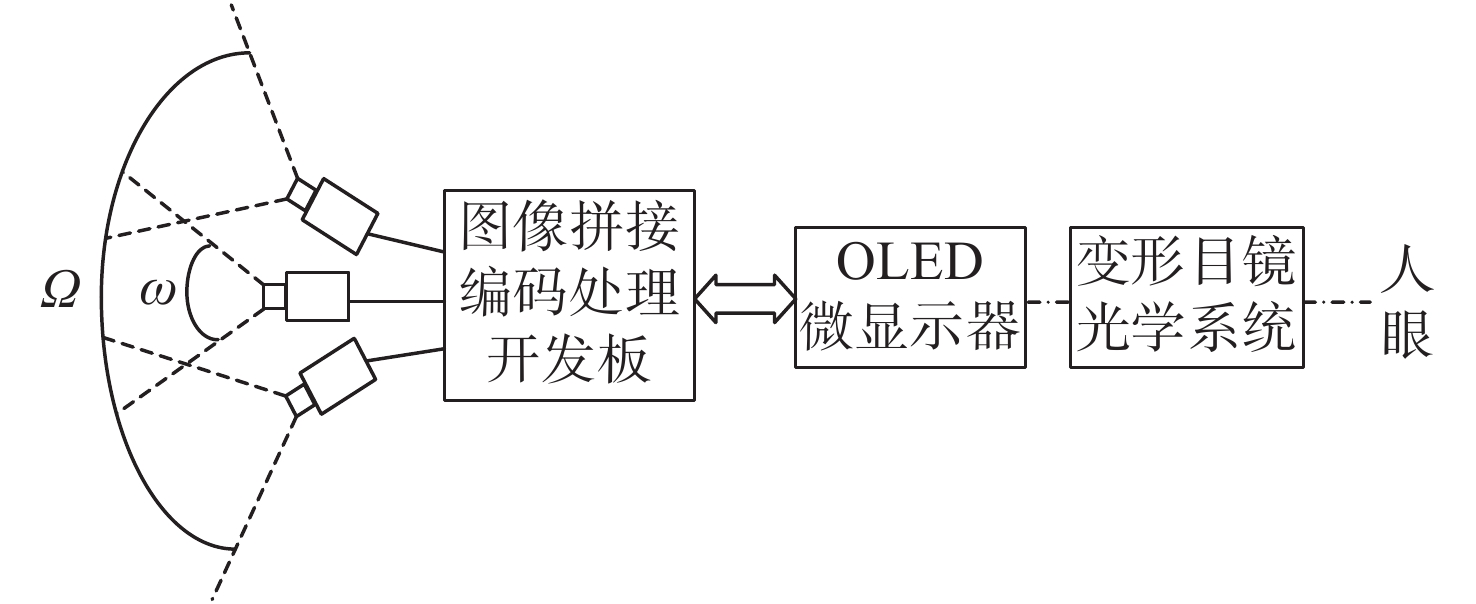

全景周视成像与显示系统由三路全景视频图像采集模块、FPGA (Field Programmable Gate Array) 图像处理模块、全景OLED (Organic Light-Emitting Diode) 微显示器和变形目镜模块以及图像显示光学模块4大部分组成,如

图 1. 全景周视成像与显示系统整体框图

Fig. 1. Overall block diagram of panoramic peripheral vision imaging and display system

2.1 凝视型全景成像系统

为同时固定3个摄像机,设计了一个由硬铝材料制成的圆弧底板,底板滑槽可使得3个相机的夹角在50°到60°之间可调节,搭建的凝视型全景成像系统如

2.2 基于OLED微显示器的全景微显示器设计

本文选用北方奥雷德公司的OLED微显示器设计全景微显示器,其为SVGA (Super Video Graphic Array) (800×600)和SXGA (Super Extended Graphics Array) (1 280×1 024) 两种分辨率模式,尺寸为0.97英寸,通过不同信号驱动板可以实现标准模拟/数字视频图像显示[8-12]。

OLED微显示器的RGB排列为将其转化为高分辨黑白全景微显示器奠定了技术基础。通过去除SVGA(800×600)彩色OLED微显示器的彩色滤光片阵列,并以每一个RGB子像素作为一个独立显示像素,可将常规的OLED微显示器转变为2400 pixel×600 pixel的黑白全景OLED微显示器(如

图 4. OLED微显示器分辨率扩展示意图

Fig. 4. Schematic diagram of resolution expansion of OLED microdisplay

2.3 变形目镜系统设计

由于OLED显示的全景图像的纵横比为原来的1/3,为适应人眼观察,需设计变形目镜系统对压缩图像进行还原。

虽然针对性地设计和制作变形目镜是最佳的方案,但作为技术途径的验证以及应用背景的引导,选用了现成的车载夜视系统的大目镜+变形镜的方案,系统结构示意图如

图 5. 变形目镜光学系统整体结构示意图

Fig. 5. Schematic diagram of the overall structure of anamorphic eyepiece optical system

最终变形成像透镜组的光学总长为249.3 mm,视场为10.13 mm×7.61 mm,与OLED微显示器有效显示区域尺寸一致,工作波段为400~700 nm。

2.4 视频图像采集

全景图像的获取由安装在圆弧支架水平布局且同步控制的3个低照度工业摄像机实现,如

凝视型全景视频图像采集系统通过3个摄像机采集到3幅720 pixel×576 pixel的视频图像。根据重叠视场角δ与摄像机视场角φh的比例关系,计算出相应的非像素重叠区域S为:

2.5 FPGA的全景图像拼接实现

系统的全景图像拼接处理功能主要是以图像校正算法、基于双线性插值法的图像缩放算法以及图像平移相关算法为基础,结合全景成像的图像拼接以及FPGA硬件处理平台特点进行优化,将3幅视频图像拼接为1幅全景数字图像,并按照OLED微显示器的像素灰度驱动重新编码,驱动OLED显示器进行全景图像显示。由于充分考虑了图像特征,使得处理过程避免了大规模的运算,同时保证拼接的有效性。

FPGA处理平台基于Xilinx公司Spartan-6系列XC6SLX45芯片,具有6822个Slice,58个DSP 48A1 Slice,401 KB分布式RAM及2088 KB块 RAM,最大用户I/O为358个,满足设计需求[22-26]。FPGA处理平台是系统核心,在其上不仅实现了全景视频图像采集与拼接处理算法的实时处理,而且将全景视频图像采集系统与全景视频显示系统连接为一个统一的全景成像与显示系统[27-31]。

显示系统采用的是800×600彩色OLED微显示器,其得到的视频信号远大于可以显示的有效值,同时视频图像在摄像机成像过程中存在畸变。因此,先对图像进行畸变校正和图像缩放处理。

对图像进行畸变校正操作,畸变模型为:

其中,k1,k2表示的是径向畸变参数,(

利用MATLAB标定工具Camera Calibrator 来完成整个标定过程。这种标定工具是基于张正友先生提出的标定方法进行标定的,可得到对应的参数值,如本次标定得到的径向畸变参数

然后,根据双线性插值法计算得到每一个坐标点校正后的像素值,

假设p (x, y)为未知函数f中一个点,为了得到P (x, y)的值,假设已知

算出P1点和P2点的函数值,接着,在y方向对二者进行线性插值。得到:

将720 pixel×576 pixel大小的3幅畸变图像分别存储在DDR3中。对畸变图像像素坐标取整,假设得到的一个像素坐标为(u, v),则其他3个坐标分别为(u+1, v),(u, v+1),(u+1, v+1)。根据坐标与DDR3的存储关系就能得到想要的4个像素坐标在DDR3中的存储地址,进而得到对应的灰度值。最后,根据双线性插值法计算得到校正后图像每一个像素点的像素值。

由于OLED显示屏的分辨率为800 pixel×600 pixel,为了在OLED显示屏上完全成像,需要将得到的视频图像在水平方向上缩小为原来的1/3,使得整个全景图像都能成像到OLED显示屏上。图像缩放同样是基于双线性插值法来完成的。该算法至少需要两行数据才能开始计算。在图像缩放之前,原始的视频图像存储于DDR3中,用读写异步的FIFO来缓存视频数据。根据需要,用两组8比特宽度和1024深度的RAM来存储亮度数据,两个8比特位宽,深度为512的RAM存放色差数据。

图像处理完成之后,需要将有效图像数据按顺序输出。由于OLED显示的是RGB视频信号,因此需将信号从YCbCr42视频信号转换为RGB视频信号,然后通过alpha算法根据重叠区域的大小与位置,将有效的视频信号输出显示于OLED显示屏。

3 实验系统成像效果及其分析

研制的全景成像与显示实验系统如

图 9. 全景视频图像采集与显示实验系统

Fig. 9. Experimental system of panoramic video image acquisition and display

实验表明:本文系统和处理算法有效实现了图像的拼接,实现了动态全景场景的视频采集和显示,是一种可兼顾视场与分辨率的实用全景成像和显示模式。

为了实现技术的实用化,除需进行实用化设计外,目前系统尚存在一些有待改进之处:

(1)在两幅图像相交的地方存在一定的上下起伏,这主要由采集系统本身存在的误差及实验采集时的误差所引起。理论上来说,如果能使采集系统中的3个视频摄像头保持在同一水平线上就能使二者重合;

(2)由于没有对不同摄像机的亮度进行标定,因此在视场接缝处存在一定的亮度差异,从而形成分割线,进一步加入亮度校正后可以解决此问题;

(3)目前系统实现了150°大视场显示,进一步减小视场重叠区域以及选择不同焦距物镜或摄像机数,可进行更大(如大于180°)或更小视场的系统设计;

(4)采用6个低照度摄像机或非制冷红外相机以及1280×1024的OLED微显示器可进一步实现凝视周视成像。其是在本文的设计基础上进行拓展实现的,不过会增加采集与图像处理部分的计算,实现较为困难。

(5)将目镜和变形镜进行一体化设计可实现性能更佳、结构更为紧凑的小型化全景周视显示系统。

4 结 论

全景成像在诸多领域都有迫切的应用需求,但传统成像与显示系统之间存在视场与分辨率不可兼顾的问题,同时观测空间狭小和观察环境的动态变化也造成了诸多的不便。本文研究了一种基于变形目镜和OLED的全景周视成像与显示技术,搭建了研制实验系统。实验表明其在一定程度上对缓解视场与分辨率的矛盾具有意义,适合在狭小空间实现全景或周视场景的高分辨观察。该技术在反恐条件下的“透明装甲”技术、要地警戒、凝视型潜艇潜望观察等方面具有潜在的应用前景。

[2] BENOSMAN R, KANG S B. Panamic Vision[M]. New Yk: Springer, 2001.

[6] 徐海云, XU H Y, WANG P, 王普, 王广生, WANG G SH. Research on the realization techniques of panoramic image merging[J]. Journal of Beijing University of Technology, 2004, 30(4): 417-422.

[9] 陈敏泽, CHEN M Z, LIN Y Y, 林韵英. New development of OLED display driving technology[J]. Video Engineering, 2013, 37(S2): 419-421.

[19] 王志坚, WANG ZH J, ZHENG J P, 郑建平. The object–image conjugate theory of optical systems and optical elements in motion[J]. Journal of Changchun Institute of Optics and Fine Mechanics, 1992, 15(2): 1-13.

[22] 马其琪, MA Q Q, 鲍爱达, BAO A D. High speed and large capacity data buffer design based on DDR3 SDRAM[J]. Computer Measurement & Control, 2015, 23(9): 3112-3113, 3118.

[23] ZHOU R J, HAO Y Y, HU J S. Quick system-level DDR3 signal integrity simulation research[J]. Journal of Electronic Science and Technology, 2013, 11(3): 286-290.

[25] 马志超. DDR3控制器的设计与验证[D].西安: 西安电子科技大学, 2013.MA ZH CH. Design verification of DDR3 controller[D]. Xi’an: Xidian University, 2013. (in Chinese)

[26] 赵曙光. 可编程逻辑器件原理、开发与应用[M]. 西安: 西安电子科技大学出版社, 2000.ZHAO SH G. Principle, Development Application of Programmable Logic Device[M]. Xi’an: Xidian University Press, 2000. (in Chinese)

[28] BHASKER J. Verilog HDL综合实用教程[M]. 孙海平, 译. 北京: 清华大学出版社, 2004.BHASKER J. Verilog HDL Synthesis A Practical Primer[M]. SUN H P, trans. Beijing: Tsinghua University Press, 2004. (in Chinese)

[29] XILINX Inc. Spartan6 family overview[R]. US: Xilinx Inc, 2011.

[30] WINBOND. W25Q128FV Datasheet[R]. Winbond, 2012.

[31] 冯雁军, FENG Y J, 周清海, ZHOU Q H, 孙伟昶, SUN W CH. Design of real-time panoramic video system based on FPGA[J]. Electronic Engineering & Product World, 2013, 20(2): 72-74.

Article Outline

罗杰超, 郭俊达, 米凤文, 裘溯, 顿雄, 金伟其. 基于变形目镜和OLED的全景周视成像与显示技术[J]. 中国光学, 2020, 13(4): 752. Jie-chao LUO, Jun-da GUO, Feng-wen MI, Su QIU, Xiong DUN, Wei-qi JIN. Panoramic peripheral vision imaging and display technology based on a deformation eyepiece and OLED[J]. Chinese Optics, 2020, 13(4): 752.