基于FPGA的8通道高精度TDC技术  下载: 1377次

下载: 1377次

1 引言

时间数字转换器(TDC)技术广泛应用于激光雷达飞行时间测量、流量计、导航定位、医学成像、高精度数字示波器等领域,TDC的测量精度与这些领域的技术水平息息相关。现有TDC有两种:专用TDC芯片[1]和基于现场可编程门阵列(FPGA)实现的TDC[2-9]。专用芯片如TDC720x系列时间分辨率为55 ps,精度为35 ps,量程可达8 ms,最多支持2通道;TDC-GPX2的时间分辨率为81 ps,精度为50 ps,最多支持8通道。传统基于FPGA实现TDC测量的原理是用直接计数法,测量分辨率低于1 ns时需要使用GHz的高速时钟计时。由于带宽的限制,这种方案不适用于目前大多数FPGA芯片。2008年,美国费米实验室的吴进远等[2]提出Wave Union A 和Wave Union B的优化算法,并在Cyclone II FPGA上验证了单通道TDC的测量精度可达25 ps和10 ps。2014年Torres等[3]用CARRY4作为延迟单元,在Xilinx KC705 Kintex-7开发板上实现了24通道的TDC设计,测量均方根(RMS)可达22.7 ps,但峰峰值误差超过200 ps。相比专用集成电路(ASIC),采用FPGA实现的TDC量程大、研发成本低、周期短、灵活性高,且能实现多通道测量,因此成为TDC研究的热点。

本文针对多通道、大量程、高精度激光测距的需求,采用延迟链的方法,设计实现了基于FPGA的8通道高精度TDC,对激光雷达测距及其相关技术研究具有一定的参考价值。

2 TDC测量原理

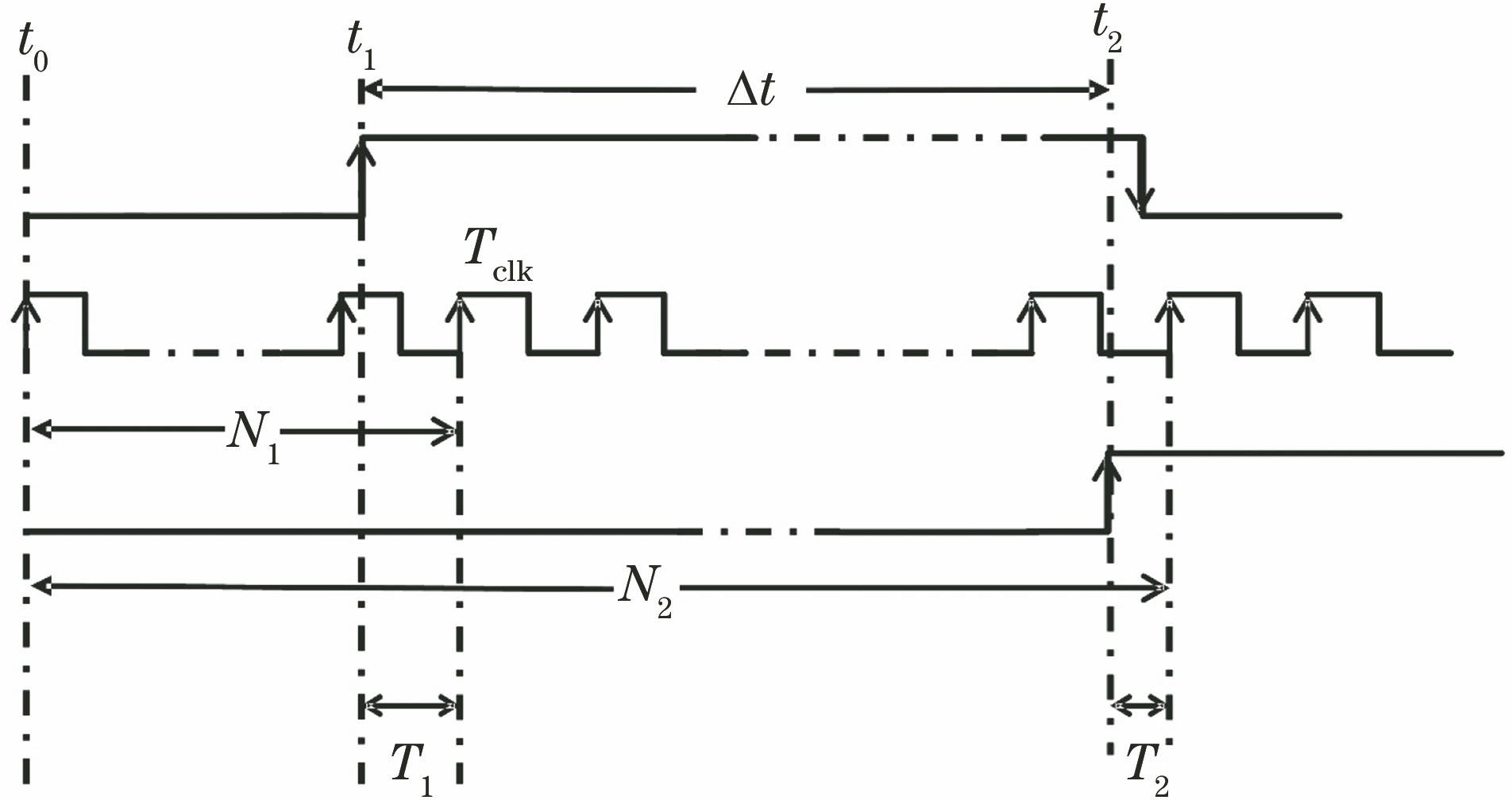

TDC测量原理如

3 多通道TDC的设计与实现

3.1 多通道TDC结构

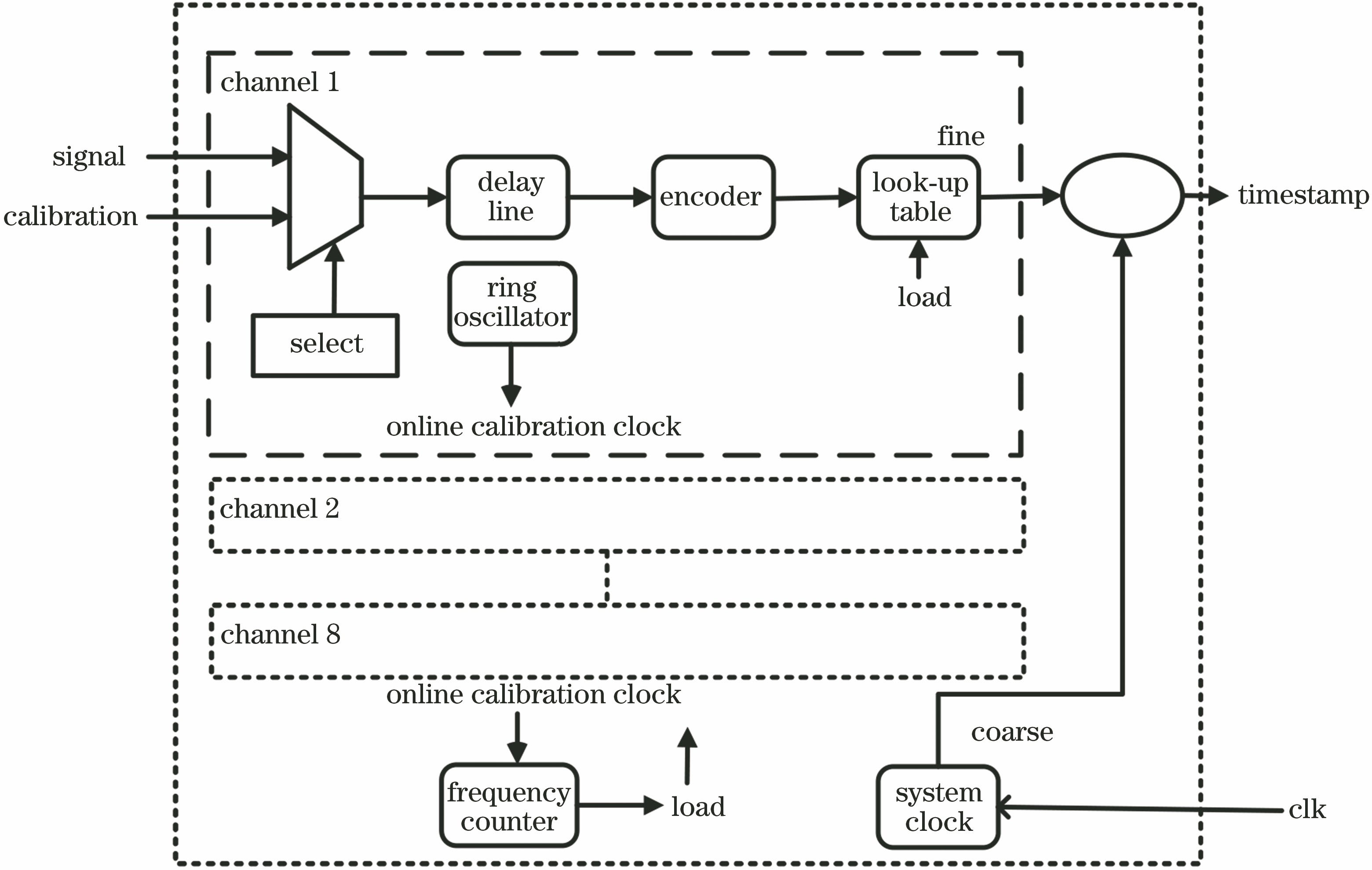

多通道TDC结构如

3.2 延迟链结构

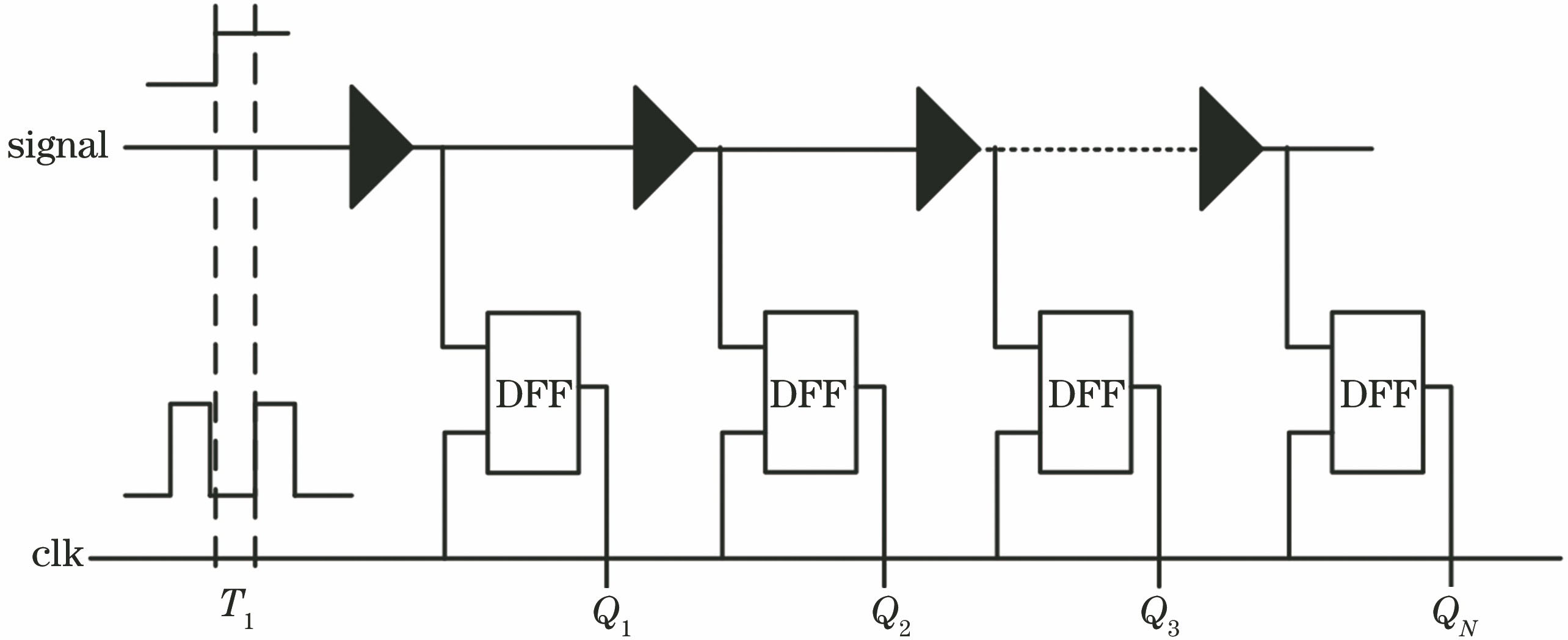

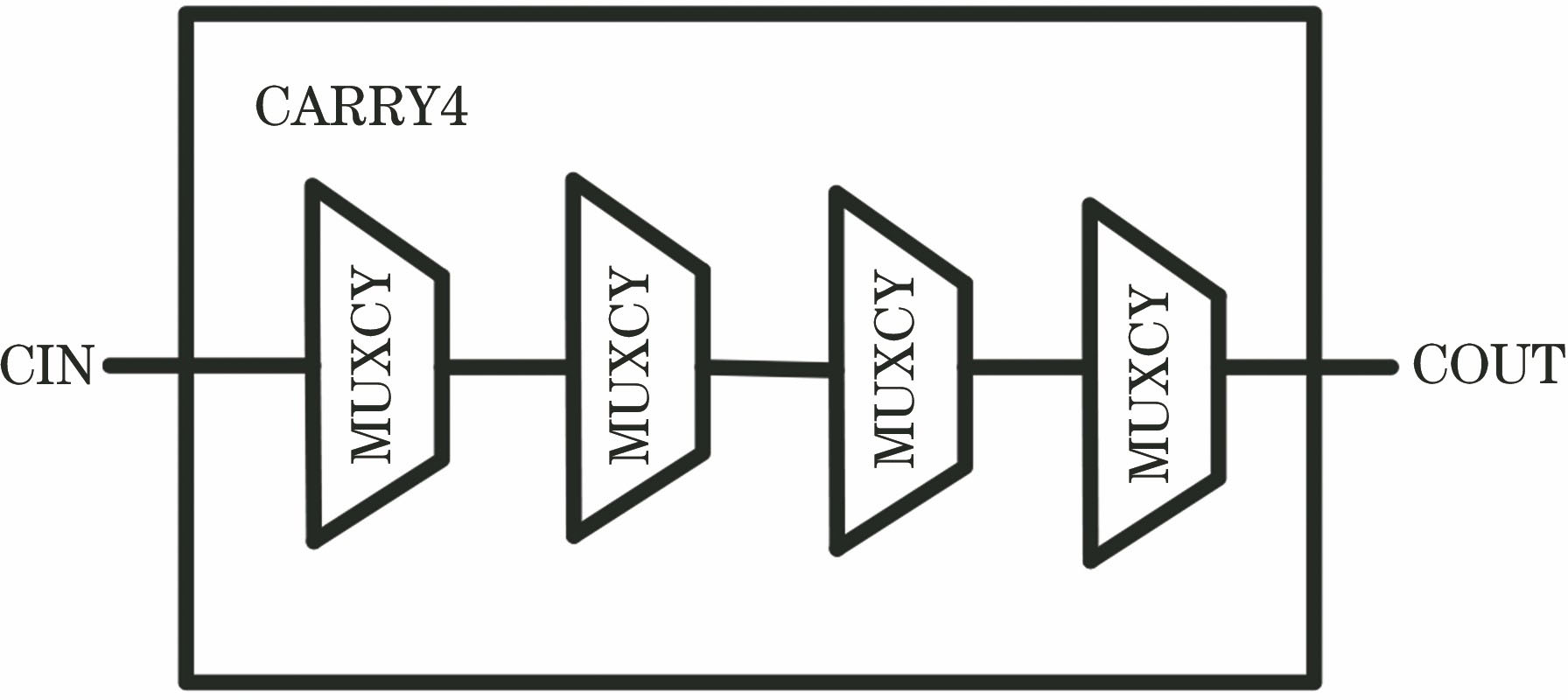

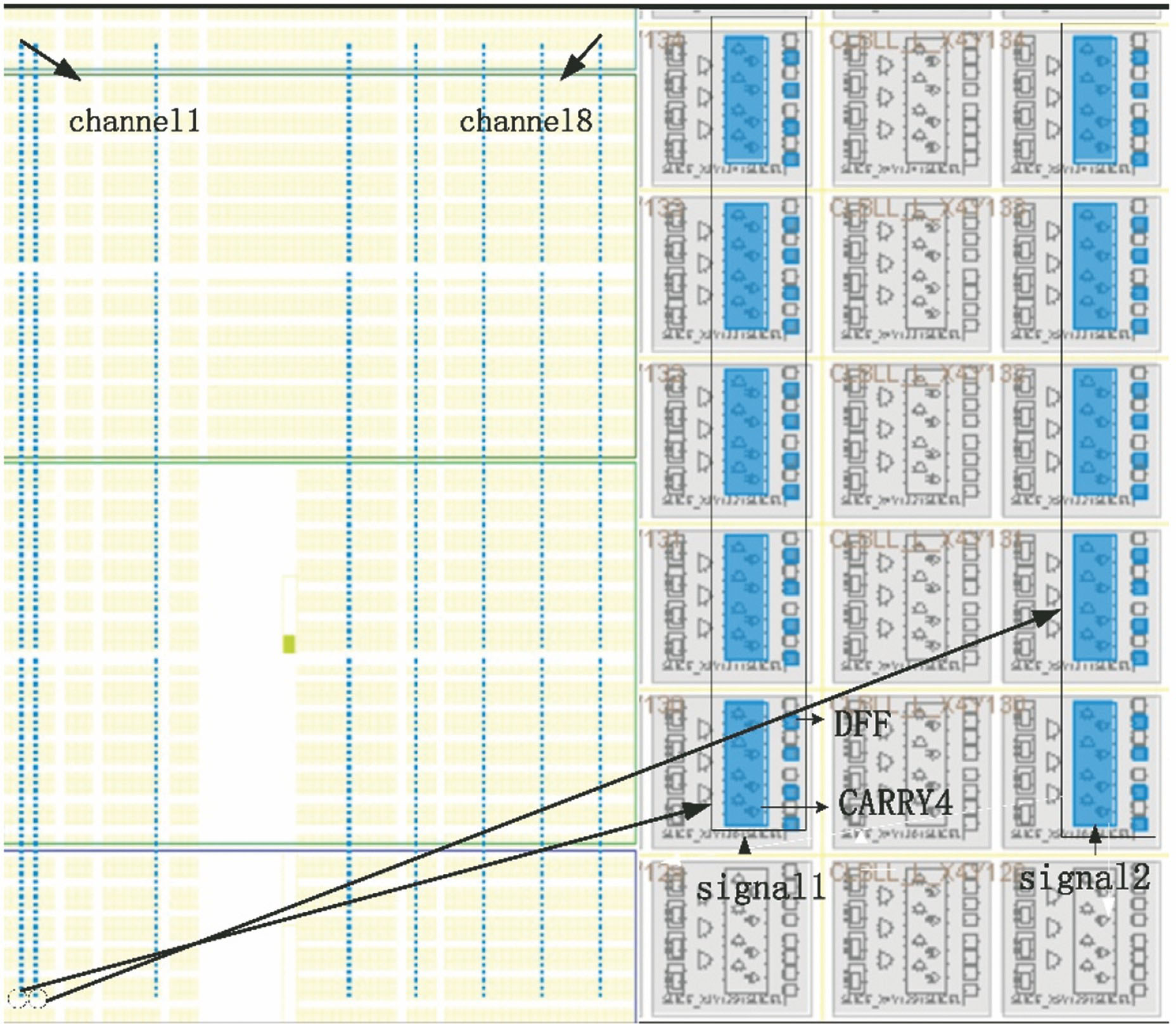

延迟链上的延迟单元对应Xilinx FPGA芯片CARRY4模块中的选通器(MUXCY)元素,如

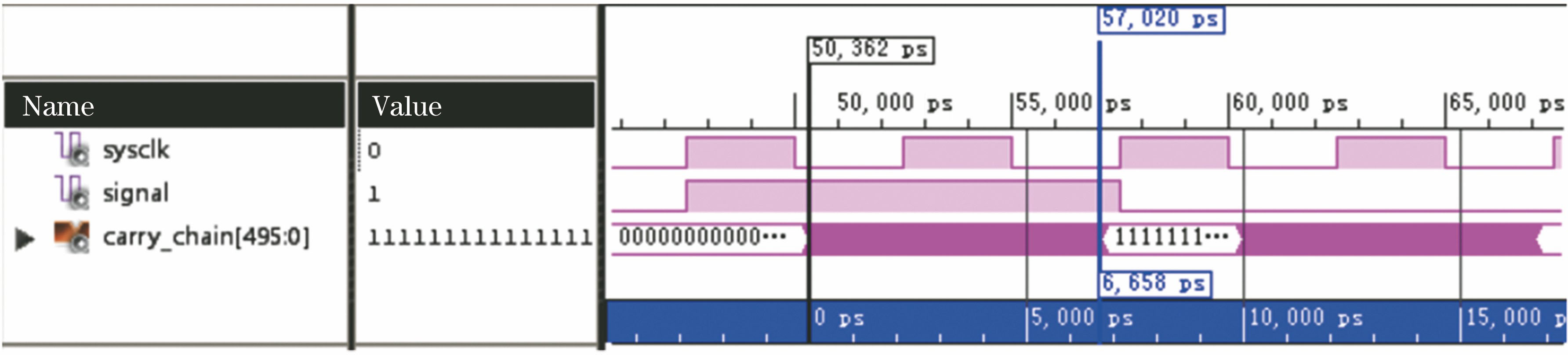

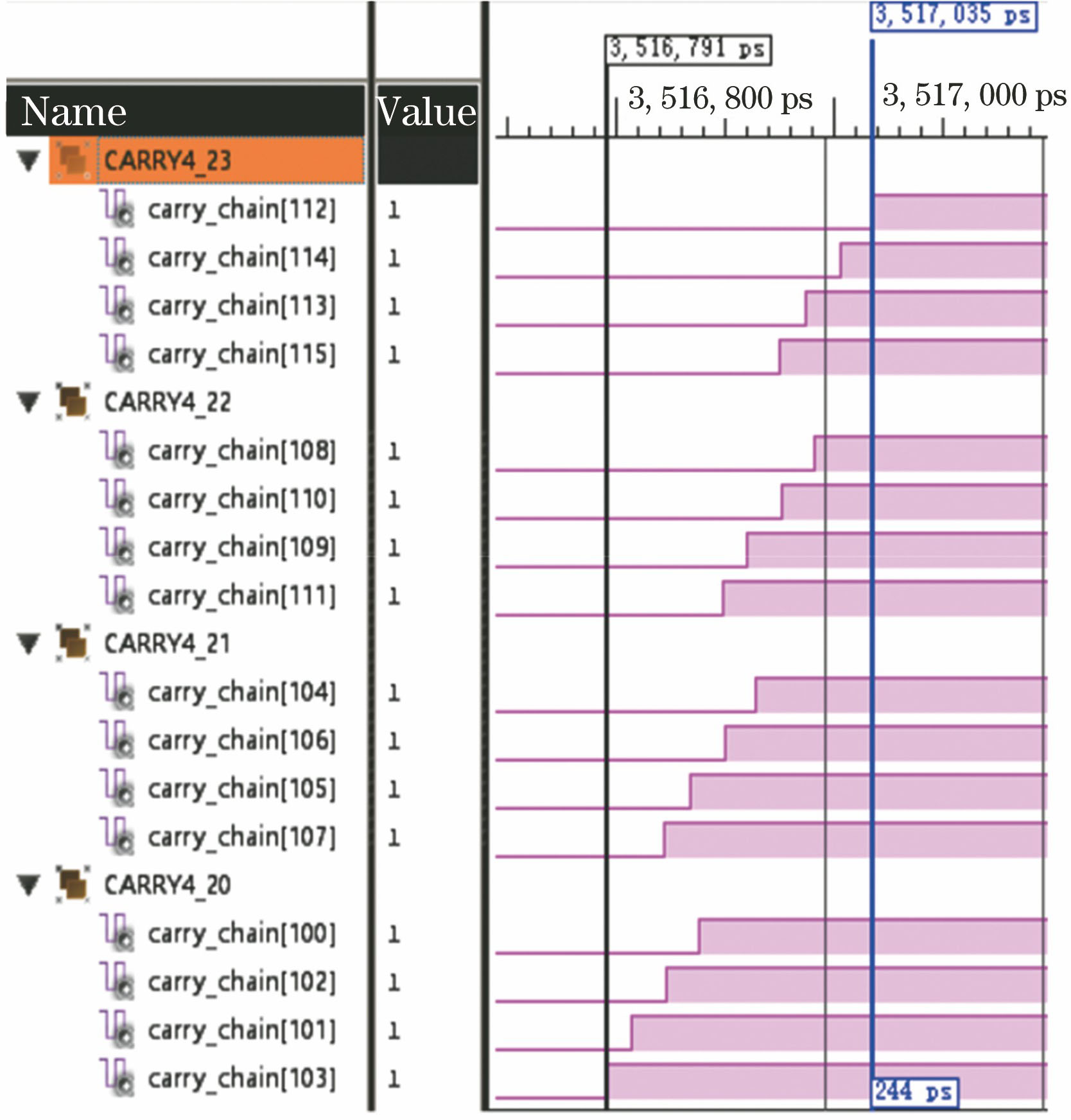

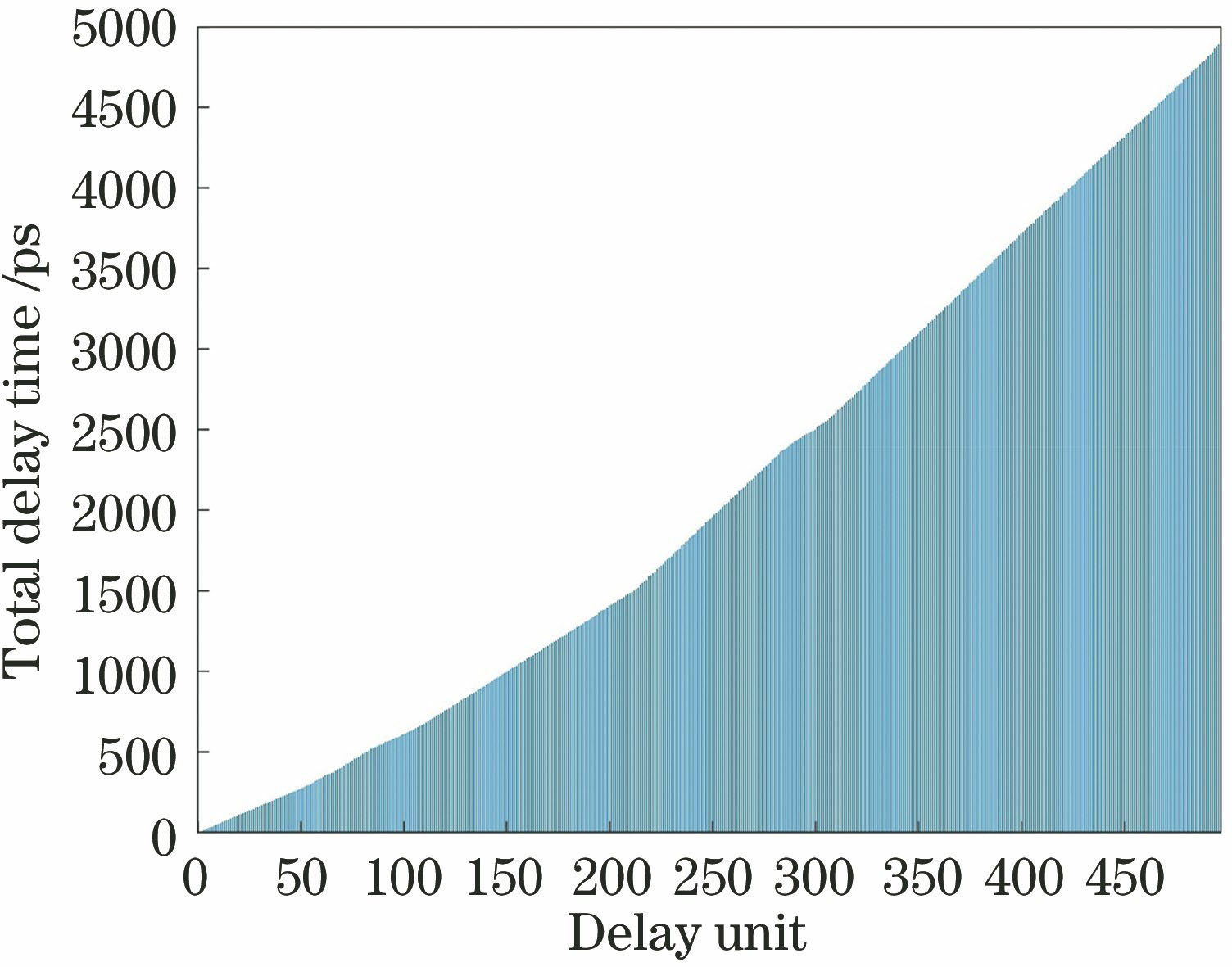

单个MUXCY元素的延迟越小,TDC的时间分辨率越好。Xilinx数据手册中,没有单独说明MUXCY的延迟时间,但有CARRY4模块的延迟时间。对于Spartan-6的-2速度类型器件,CIN到COUT的延迟时间一般为100 ps,每个CARRY4模块含有四个MUXCY,平均延迟时间为25 ps。对于Kintex-7的-1速度类型器件,CIN到COUT延迟时间一般为60 ps,平均延迟时间为15 ps,明显优于Spartan-6器件的分辨率。延迟链时序仿真结果如

3.3 TDC技术实现

如

第i个延迟单元的延迟时间τi为

式中,Ni为N次随机信号抵达第i个延迟单元累计的次数。

细计数Ti可以表示为

测量待测信号细计数的同时,需要进行在线实时校准。每个通道附近都放置若干个由31个MUXCY_1原语构成的环形振荡器,产生在线校准时钟,频率计数器观测在线校准时钟的频率变化。当延迟单元的延迟时间受温度、电压的波动而变化时,在线校准时钟的频率也会随之改变,由此可以推断出温度、电压对延迟链的影响,实时更新查找表中的延迟时间。

粗计数采用直接计数法,若待测信号signal的上升沿经过N个系统时钟周期,得到的粗计数为N×Tclk,待测信号signal的时间戳由细计数和粗计数联合得出。

4 TDC实验结果及分析

4.1 TDC测试方案

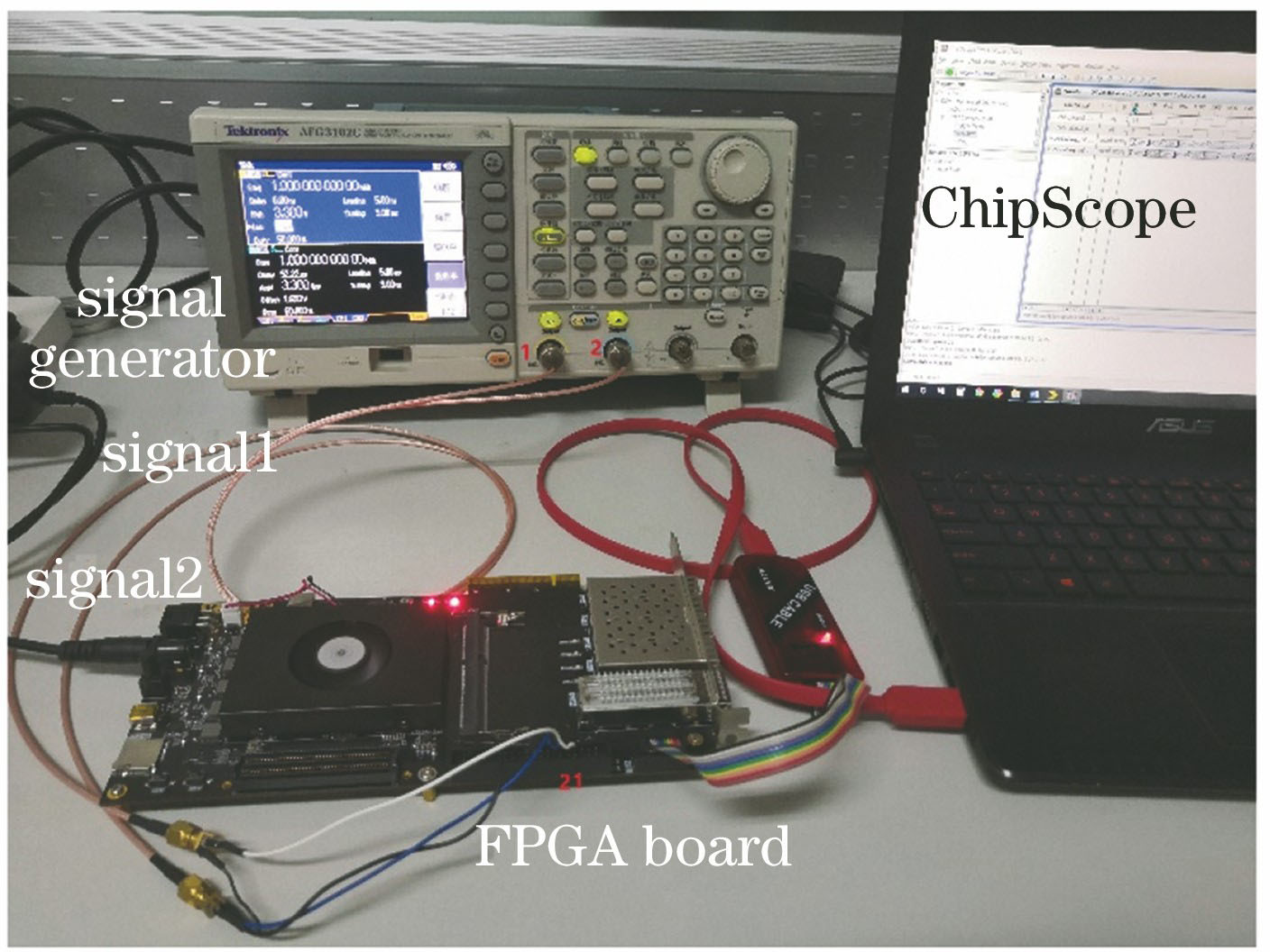

TDC测试平台如

4.2 TDC实验结果及分析

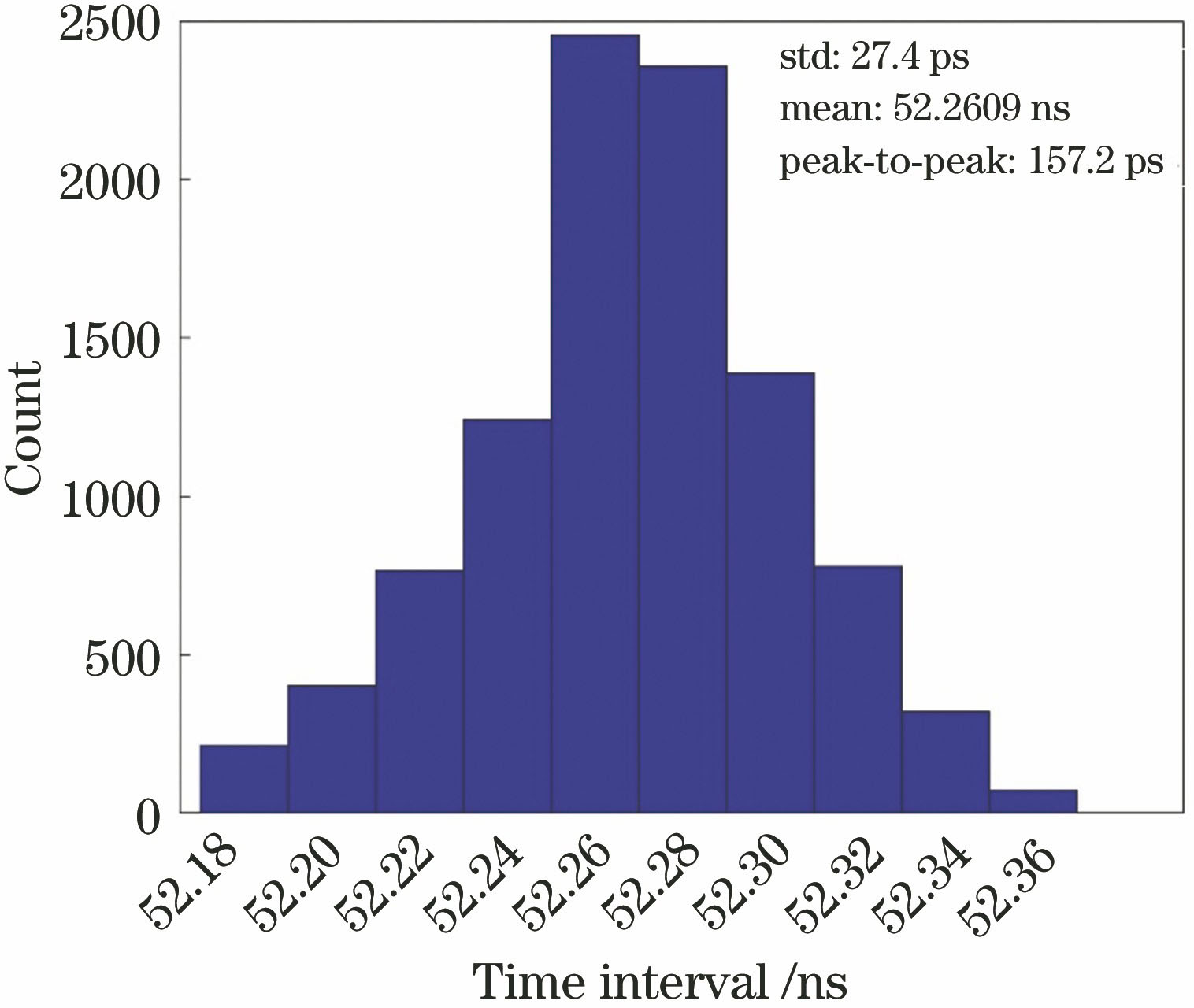

TDC的测量结果如

固定通道1的位置,改变通道2的输入位置,得到8通道的测量结果,如

表 1. 8通道测量结果

Table 1. Measurement results of 8-channel

|

5 结论

基于FPGA完成了8通道高精度TDC的设计,针对延迟链上延迟单元的非线性时延,采用码密度校准法和在线校准对细计数进行校准。所设计的TDC采用25位200 M系统时钟作为粗计数,计时量程为167.77 ms。实验结果表明,TDC的时间分辨率低于35 ps,计时精度为36.8 ps,误差峰峰值为157.2 ps。高精度的时间测量对信号输入延迟链的位置、跨时钟域处理有严格的要求,后续工作需要进行更加合理的时序约束,手动布局、布线来提高精度。同时需要在恒温箱中检测温度、电压对TDC性能的影响。

[1] 侯志军, 马红皎, 王康, 等. 基于TDC-GPX2的精密时间间隔测量仪设计[J]. 时间频率学报, 2017, 40(4): 213-220.

Hou Z J, Ma H J, Wang K, et al. Design of a precise time interval measuring instrument base on TDC-GPX2[J]. Journal of Time and Frequency, 2017, 40(4): 213-220.

[2] Wu JY, Shi ZH. The 10-ps wave union TDC: improving FPGA TDC resolution beyond its cell delay[C]∥2008 IEEE Nuclear Science Symposium Conference Record, October 19-25, 2008, Dresden, Germany. New York: IEEE, 2008: 3440- 3446.

[4] Büchele M, Fischer H, Gorzellik M, et al. A 128-channel time-to-digital Converter (TDC) inside a Virtex-5 FPGA on the GANDALF module[J]. Journal of Instrumentation, 2012, 7(3): C03008.

[7] Wu J Y. Several key issues on implementing delay line based TDCs using FPGAs[J]. IEEE Transactions on Nuclear Science, 2010, 57(3): 1543-1548.

[9] Wang J H, Liu S B, Shen Q, et al. A fully fledged TDC implemented in field-programmable gate arrays[J]. IEEE Transactions on Nuclear Science, 2010, 57(2): 446-450.

Article Outline

张孟翟, 王华闯. 基于FPGA的8通道高精度TDC技术[J]. 激光与光电子学进展, 2020, 57(13): 131203. Mengdi Zhang, Huachuang Wang. 8-Channel High Precision TDC Technology Based on FPGA[J]. Laser & Optoelectronics Progress, 2020, 57(13): 131203.