连续波输出功率111.27mW的G波段四端口平衡式倍频器【增强内容出版】

1 Introduction

As the critical solid-state sources in several terahertz applications including imaging,wireless communication and radio astronomy[1-3],Schottky diode-based multipliers have been well-developed over the past years. The coming generation of heterodyne array instruments toward frequencies up to 1 THz directly put forward the requirement of higher local oscillator(LO)output power levels especially in critical pumping frequencies to enable related array receivers [4]. Generally,terahertz solid-state sources rely on several individual multipliers in cascade to achieve enough frequency multiplication,in which the efficiency and output power of each stage directly affect the overall performances. For example,the generation of powers at frequencies up to 670 GHz put forward the urgent requirements on sufficient powers over 200~230GHz range. Thus,improving the power-handling capabilities as well as conversion efficiencies have been a research focus of diode-based multipliers.

At the moment,the classical balanced doublers[5,6]proposed by Erickson are preferred for the inherent suppression on odd-order harmonics,whose power handling-capabilities are restricted by the limited diode numbers. As a result,the power-combined techniques become one of the most preferred methods improving the overall power-handling capabilities,at the expense of non-negligible decreases in conversion efficiency [7-9]. And the overall efficiency of power-combined doublers would also degrade with the increase of multiplying channels,which restricts the highest achievable output power. Thus,developing novel doubling configurations,which can increase the circuit power-handling capabilities with improved conversion efficiencies,becomes an attractive solution for high power terahertz multiplying sources.

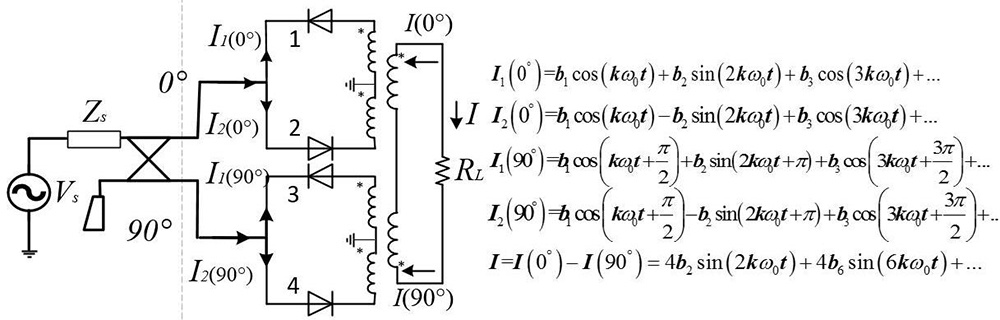

In this letter,a novel four-port balanced doubler prototype presented in our recent work[10] has been introduced to break through the achievable output power in G-band(as shown in

图 1. 四端口平衡倍频原型及相关谐波电流图

Fig. 1. Diagram of the four-port balanced doubler prototype and related harmonic currents[10].

1 Configuration and design

According to the ideal prototype in

To implement the 220 GHz balanced doubler,four discrete GaAs Schottky diodes have been utilized. As shown in

图 3. (a)二极管结区的剖面图,(b)二极管三维示意图

Fig. 3. (a)Corss section view of the diode junction,(b)3D-view of the diode

In addition,self-heating and current saturation effects under high operation power must be taken into consideration for better simulation accuracy. A self-consistent electro-thermal model is developed to optimize high efficiency circuits from both the electrical and thermal perspectives. The electrical model of the diode,as well as the self-heating effects characterization,are similar to that in Ref.[12]. Differently,the temperature-dependent junction parameters,including saturation current(Is),ideality factor(η)and series resistance(Rs),are extracted based on temperature-controlled I-V measurements rather than simply approximating with theoretical expressions[8]. Utilizing the same test setup in [9],the measured I-V and C-V curve of a 3-anode diode under different temperature levels are illustrated in

图 4. 在不同温度梯度条件下测试的二极管I-V曲线(a)和C-V曲线族

Fig. 4. Measured diode I-V curves (a) and C-V curves (b) at different temperature levels.

On the one hand,the constant zero-bias junction capacitance is extracted to be 32fF with C-V curves,featuring low dependency on junction temperatures. On the other hand,the temperature-dependent saturation current(Is),ideality factor(η)and series resistance(Rs)could be calculated and extracted based on the temperature-controlled I-V curves,utilizing the extraction method discussed in our previous work[9]. And the extracted and fitted temperature-dependent parameters are illustrated in

图 5. (a)提取和拟合的随温度变化的串联电阻; (b)理想因子和饱和电流曲线

Fig. 5. (a)The extracted&fitted temperature-dependent series resistance; (b)ideality factor and saturation current.

Thermal resistance matrix of the multiplier circuit also need to be extracted to establish the dependency between thermal and electrical domain(shown in

图 6. (a) 倍频电路热仿真截面示意图,(b) 热阻抗矩阵主要对角元随温度的变化曲线,(c) 根据仿真热阻抗矩阵预测的结温随耗散功率变化曲线

Fig. 6. (a) Cross section views diodes mounted in the cavity,(b) The main diagonal terms in the calculated thermal resistance matrix,(c) Predicted anode temperatures as a function of dissipated power

The optimum embedding impedances presented to different harmonics at each junction is determined for maximum conversion efficiency with an input power of 25.5 dBm. With the consideration of self-heating effect,the whole circuit is analyzed and optimized with the cooperation of electro-magnetic and harmonic balance simulations. This process is iterated,modifying the circuit geometry each time,to push the impedances presented to each anode close to their optimum values.

图 7. 装配后的220 GHz四端口平衡倍频器模块细节图,(b) 四端口二倍频电路的管结阻抗匹配结果图,(c) 传统倍频器的照片

Fig. 7. (a) Details of the fabricated 220 GHz four-port balanced doubler module,(b) Impedance matching in the four-port and conventional circuit,(c) Photograph of the conventional doubler

2 Fabrication and Measurement

The fabricated 220 GHz balanced doubler is shown in

图 8. (a)传统平衡式倍频的测试性能,(b)不同偏置下四端口倍频电路的输出功率和倍频效率

Fig. 8. (a) Performance of the traditional doubler,(b) Output powers and efficiencies of the four-port circuits under different bias.

It is difficult to evaluate the efficiencies of these two doublers under different operation powers. Thus,a comparison of the efficiencies as a function of dissipated power in each diode(DPID)need to be conducted. In

表 1. 相近频段的平衡式二倍频电路对比

Table 1. Comparison of balanced doublers in adjacent frequencies

|

图 9. (a)在相同的DPID条件下的两种模块性能对比,(b)在相同输入功率条件下的两种模块对比

Fig. 9. (a) Comparison of these two modules at the same DPID,(b) Comparison of these two modules as a function of input power

3 Conclusions

In summary,the proposed novel four-port doubler has been developed,featuring a peak efficiency of 39.5% at 218 GHz in continuous waves. And the proved peak output power is 111.27 mW at 225.8 GHz,which reaches the highest diode-based multiplying power reported in this range to the author’s knowledge. This topology also exhibits improved efficiency than the conventional one with doubled power-capability. Thus,this configuration holds great potential in developing high power sources for modern radar systems and other terahertz applications.

[1] (崔振茂, 高敬坤, 陆彬, 等. 340 GHz稀疏MIMO阵列实时3-D成像系统. 红外与毫米波学报)2017, 36(1): 102-105.

Cui Zhen-Mao, Gao Jing-Kun, Lu Bin, et al. Real time 3D imagiog system based on sparse MIMO array at 340 GHz[J]. J.Infrared Millim.Waves.

[5] EricksonN., “High efficiency submillimeter frequency multipliers, “in IEEE Int. Microwave Symp. Dig., San Diego, CA, 1990, pp.1301-1304.

黄昆, 杨昊, 李若雪, 周人, 蒋均, 何月, 田遥岭. 连续波输出功率111.27mW的G波段四端口平衡式倍频器[J]. 红外与毫米波学报, 2024, 43(1): 79. Kun HUANG, Hao YANG, Ruo-Xue LI, Ren ZHOU, Jun JIANG, Yue HE, Yao-Ling TIAN. G-band quad-port balanced multiplier with 111.27mW continuous-wave output power[J]. Journal of Infrared and Millimeter Waves, 2024, 43(1): 79.