二维光子晶体全光逻辑门的设计与仿真  下载: 1271次

下载: 1271次

1 引言

光子晶体是介电常数不同的几种材料在空间中按一定规律排列的人工合成材料,具有光子禁带和光子局域两大特性[1-2]。依据这些特性设计了许多应用价值很高的通信器件,如光开关[3]、光分束器[4]、光波分复用器[5]和光纤传感器[6]等,其制作工艺简单、易于集成,具有很好的应用价值。

全光集成电路由于在光计算机、高速数据处理和光网络等方面的突出性能,近年来越来越受到人们的重视[7]。光子晶体对光集成电路中的光逻辑门的小型化起着重要作用。目前,基于光子晶体实现逻辑门的主要方法有自准直效应[8-9] 、多模干涉效应[10-11]和非线性效应[12-13]等技术。自准直光束门需要在门的输入端设置一个移相器来实现逻辑运算,这将导致器件尺寸较大;多模干涉逻辑门对于不同的逻辑门,耦合长度不同且都需要精确的控制,故其结构变得复杂,增大了工艺难度[14];基于非线性材料的光子晶体逻辑门具有逻辑“1”和逻辑“0”的高对比度,但因为功耗高、相互作用时间长等限制了其应用。

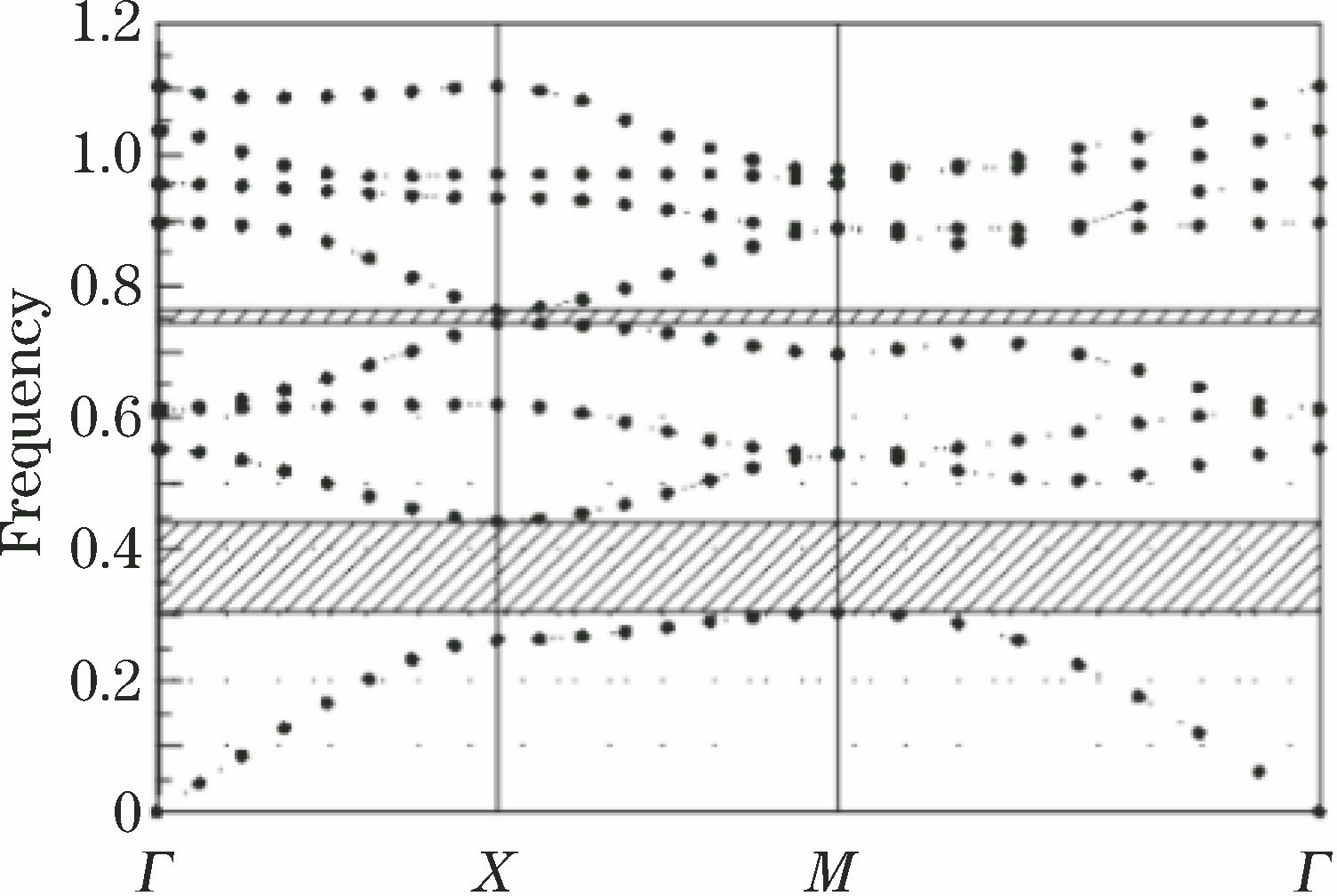

本文利用二维光子晶体环形腔与微腔的耦合特性,设计了几种二维光子晶体全光逻辑门器件。通过引入两束输入光波在耦合腔内的光程差,产生相应的相位差,从而导致光的相长干涉和相消干涉,实现了与、或、非、异或等逻辑功能。用平面波展开法和时域有限差分法分析讨论器件的能带结构和场分布情况,通过光信号功率表示逻辑值并对其逻辑功能进行验证,结果显示,所设计的器件不仅物理尺寸小,而且响应快,在集成光学领域具有潜在的应用前景。

2 理论与工作原理

基于光子晶体逻辑门的工作原理为干扰效应的利用。在空气中填充正方晶格排列的硅介质柱以构成二维光子晶体结构,介质柱折射率

根据光波导理论,如果两束光波之间的相位差为2

为了获得光的传输情况,用时域有限差分法对设计的逻辑门结构进行模拟分析,采用TM模式的高斯光源入射,宽度为1.2 μm,工作波长范围为1.3~1.7 μm,为保证仿真精度和减小数值色散,网格尺寸大小需小于

3 结构设计与仿真分析

3.1 或门(OR)

为了设计基于光子晶体的光逻辑或门,在完整光子晶体中通过直接移除介质柱制作2条输入波导、1条输出波导、1个3×3的环形腔和1个微腔,微腔半径

图 3. 或门的模拟场分布图。(a) IA=0,IB=1;(b) IA=1,IB=0;(c) IA=1,IB=1

Fig. 3. Simulated field distributions of OR gate. (a) IA=0, IB=1; (b) IA=1, IB=0; (c) IA=1, IB=1

图 4. 或门的性能变化图。(a)输出端透射率分布;(b)时间响应曲线

Fig. 4. Performance variations of OR gate. (a) Transmittance of out port; (b) curve of time response

表 1. 或门真值表

Table 1. Truth table of OR gate

|

3.2 与门(AND)

设计的逻辑与门结构如

图 6. 与门的模拟场分布图。(a) IA=0,IB=1;(b) IA=1,IB=0;(c) IA=1,IB=1

Fig. 6. Simulated field distributions for AND gate. (a) IA=0, IB=1; (b) IA=1, IB=0; (c) IA=1, IB=1

图 7. 与门的性能变化图。(a)输出端透射率分布;(b)时间响应曲线

Fig. 7. Performance variations of AND gate. (a) Transmittance of out port; (b) curve of time response

表 2. 与门真值表

Table 2. Truth table of AND gate

|

3.3 异或门(XOR)

对与门结构采用非对称结构进行改进,得到异或门,其尺寸约为14.3 μm×11 μm。因为从数字电路异或真值表中得到,如果两个输入信号都存在,则输出逻辑“0”,这意味着两个输入信号应该发生相消的干扰,可通过控制端口A和B分别到输出端的路径长度不同来实现。设计的异或门结构如

图 9. 异或门的模拟场分布图。(a) IA=0,IB=1;(b) IA=1,IB=0;(c) IA=1,IB=1

Fig. 9. Simulated field distributions of XOR gate. (a) IA=0, IB=1; (b) IA=1, IB=0; (c) IA=1, IB=1

图 10. 异或门的性能变化图。(a)输出端透射率分布;(b)时间响应曲线

Fig. 10. Performance variations of XOR gate. (a) Transmittance of out port; (b) curve of time response

表 3. 异或门真值表

Table 3. Truth table of XOR gate

|

在异或门基础上,将端口B作为控制端口且一束光以逻辑“1”入射,若端口A无光信号输入,则输出端检测到逻辑“1”;若端口A有光信号输入,则输出端检测到逻辑“0”,即实现了非门的逻辑功能。

3.4 或非门(NOR)

或非门的设计,主要根据非门的思想,通过在异或门的一个输入端级联一个或门,另一个输入端接入一个参考控制信号(Ref)逻辑“1”控制,其逻辑过程为

式中,

利用时域有限差分法对其结构进行模拟分析,得到如

图 12. 或非门的模拟场分布图。(a) IA=0,IB=0;(b) IA=0,IB=1;(c) IA=1,IB=0;(d) IA=1,IB=1

Fig. 12. Simulated field distributions of NOR gate. (a) IA=0, IB=0; (b) IA=0, IB=1; (c) IA=1, IB=0; (d) IA=1, IB=1

图 13. 或非门的性能变化图。(a)输出端透射率分布;(b)时间响应曲线

Fig. 13. Performance variations of NOR gate. (a) Transmittance of out port; (b) curve of time response

表 4. 或非门真值表

Table 4. Truth table of NOR gate

|

3.5 与非门(NAND)

其逻辑过程为

其场分布如

图 15. 与非门的模拟场分布图。(a) IA=0,IB=0;(b) IA=0,IB=1;(c) IA=1,IB=0;(d) IA=1,IB=1

Fig. 15. Simulated field distributions of NAND gate. (a) IA=0, IB=0; (b) IA=0, IB=1; (c)IA=1, IB=0; (d)IA=1, IB=1

图 16. 与非门的性能变化图。(a)输出端透射率分布;(b)时间响应曲线

Fig. 16. Performance variations of NAND gate. (a) Transmittance of out port; (b) curve of time response

表 5. 与非门真值表

Table 5. Truth table of NAND gate

|

4 结论

提出一种新的全光逻辑门的设计方法,利用光子晶体的光子禁带特性,与环形谐振器相结合,引入光程差,并对其精确控制,导致信号产生不同的相位而发生相长干涉和相消干涉,大大提高了器件的时间响应速度。用平面波展开法分析完整光子晶体的能带结构,并用时域有限差分法分析特定频率的传输情况和场分布情况,对其逻辑功能进行验证。模拟分析结果表明,各逻辑器件对比度高,均在7.3 dB以上,且器件尺寸小,时间响应快,均在218 fs以内,在集成光器件领域具有潜在的应用价值。

[2] 刘继平, 李海波, 孟祥东, 等. 含点缺陷二维函数光子晶体的本征场分布[J]. 中国激光, 2018, 45(8): 0803001.

[3] 梁龙学, 张晓金, 吴小所, 等. 基于磁光子晶体的太赫兹滤波器和光开关[J]. 光学学报, 2018, 38(5): 0513002.

[4] 李绪友, 许振龙, 刘攀, 等. 短长度超高消光比双芯光子晶体光纤偏振分束器[J]. 中国激光, 2015, 42(6): 0605006.

[5] 李旭, 乐孜纯. 光子晶体微腔稀疏波分解复用器的设计与模拟[J]. 光子学报, 2014, 43(s1): 0123003.

[6] 李佳欢, 裴丽, 王建帅, 等. 基于光子晶体光纤表面等离子体共振的温度和磁场双参量传感器[J]. 中国激光, 2019, 46(2): 0210002.

[7] 张莹, 陈梅雄, 李莹颖, 等. 光学微腔的应用和发展前景[J]. 激光与光电子学进展, 2015, 52(4): 040002.

[14] 张晓金, 梁龙学, 吴小所, 等. 二维光子晶体全光异或门的设计及研究[J]. 发光学报, 2018, 39(12): 1772-1777.

Article Outline

刘振, 吴蓉, 严清博, 吴小所. 二维光子晶体全光逻辑门的设计与仿真[J]. 激光与光电子学进展, 2019, 56(18): 182301. Zhen Liu, Rong Wu, Qingbo Yan, Xiaosuo Wu. Design and Simulation of Two-Dimensional Photonic Crystal All-Optical Logic Gates[J]. Laser & Optoelectronics Progress, 2019, 56(18): 182301.