一种改进的基于110 GHz在片S参数测试的HEMT器件寄生电阻提取方法

1 Introduction

Accurate extrinsic resistances extraction for modeling InP HEMT devices is a crucial step in the design and production of high-yield,low-cost millimeter wave circuits[1]. The common used methods mainly include numerical optimization method,cold FET method and cutoff method. In optimization method,the extrinsic resistances extraction result strongly depends on the initial value and suffers from non-uniqueness and non-physical meaning[2]. In cold FET method,the large gate currents caused by forward-biased run through the gate Schottky junction,which leads to degradation of the gate[3-6]. To avoid degradation of device characteristics,some authors proposed cutoff method to extract extrinsic resistances. However,this method is valid only at high frequency(>18GHz),and the extracted resistances fluctuate widely over the whole frequency range of interest[7-9].

In order to overcome these limitations,an improved method for determination of extrinsic resistances is proposed. In contrast with previous publications,this extraction method offers the following advantages.

1)Under operating bias point(Vgs > Vth,Vds = 0 V),the effect of channel between source and drain can be modeled by resistance Rch,while the capacitance will be dominant under cutoff bias condition.

2)The semi-analytical method which is a combination of optimization method and analytical direct extraction method has been used to determine the extrinsic resistances.

3)This extraction method is verified with S-parameters on-wafer measurement up to 110 GHz.

Section Ⅱ gives the equivalent circuit model under operating bias point(Vgs > Vth,Vds = 0 V)as well as the derivation of analytical expressions. Section Ⅲ gives the procedure of intrinsic parameters extraction. The measured and simulated results are presented in Section Ⅳ. The conclusion is given in Section Ⅴ.

1 Extrinsic resistances extraction

1.1 Equivalent circuit model

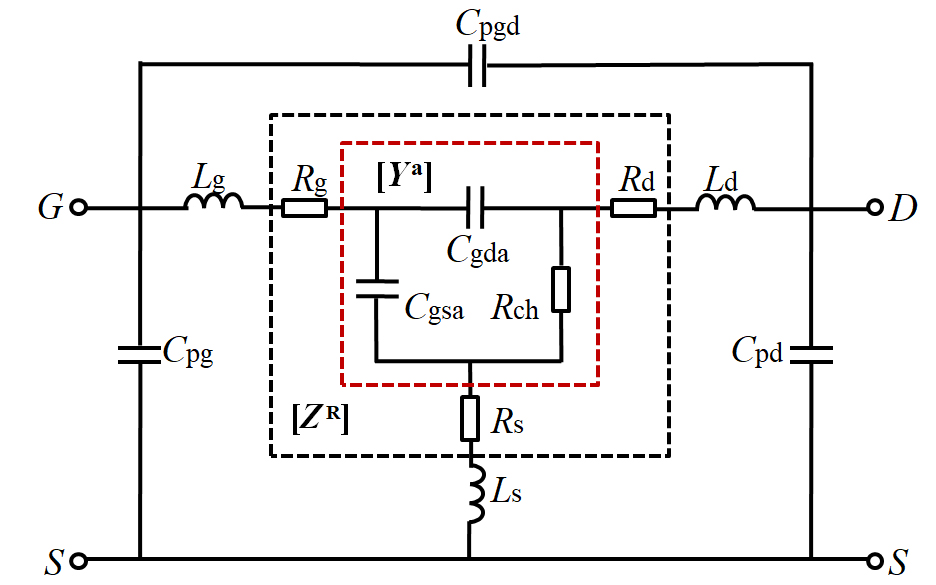

图 1. 偏置点(Vgs > Vth,Vds = 0 V)下的小信号等效电路模型

Fig. 1. The small-signal equivalent circuit model under operating bias point(Vgs > Vth,Vds = 0 V)

The intrinsic part of the equivalent circuit model,which exhibits a PI topology,so it is convenient to describe it by a Y matrix as:

Convert

The Z-parameters of intrinsic part with extrinsic resistances can be expressed as following:

Therefore,we have

By neglecting the high order term

where

Cgsa and Cgda can be determined at low frequencies:

1.2 Extrinsic parameters extraction

The pad capacitances can be determined by measuring an open test structure:

The extrinsic inductances Lg,Ld,and Ls can be determined from the imaginary part of Z-parameters(transformed from measured S-parameters)of the short test structure directly:

The extraction of extrinsic resistances can be based on the semi-analytical method which is a combination of optimization method and analytical direct extraction method. The extraction procedure is as follows.

1)De-embedding the pad capacitances and feedline inductances.

2)Set the initial value of the channel resistance Rch .

3)Calculate the extrinsic resistances Rg,Rd,and Rs using(13)-(15)which can be expressed as functions of Rch as well as frequency.

4)Set error criteria as follows:

Where

5)If error criteria are small enough,the iterative process will be end.

2 Intrinsic parameters extraction

The small-signal circuit model of intrinsic part of InP HEMT devices is illustrated in

with

From the analytical expressions(27)-(30),the intrinsic element values can be obtained directly.

3 Results and discussion

In this paper,70 nm InP HEMT devices have been used with 2×30 μm gate width(number of gate fingers×unit gate width). The S-paremeters on-wafer measurement up to 110 GHz using N5247 network analyzer with DC bias by an Agilent B1500A.

图 4. 半分析方法和截止方法提取的寄生电阻数值对比

Fig. 4. Extracted extrinsic resistances using the proposed semi-analytical method and cutoff method

表 2. 寄生电容和寄生电感数值

Table 2. The values of extrinsic capacitance and inductance

|

表 3. 本征元件数值

Table 3. The values of intrinsic parameters

|

表 4. S参数精度

Table 4. Accuracy of S-parameters

|

The intrinsic elements listed in

图 5. 1 GHz ~110 GHz 频率范围内多偏置下模拟和测量S参数对比曲线

Fig. 5. Comparison between simulated (lines) and measured (squares) S-parameters over the frequency range going:from 1 GHz to 110 GHz under multi bias

4 Conclusion

An approach for determination of extrinsic resistances for 70 nm InP HEMT devices is proposed in this paper. Extrinsic resistances are described as functions of the intrinsic channel resistance,and optimum values can be obtained using semi-analytical method under operating bias point(Vgs > Vth,Vds = 0 V). Verification of this extraction method is presented by the good agreement between the simulated and measured S-parameters under multi bias over the frequency range up to 110 GHz.

[6] Jeon M Y, Kim B G, Jeon Y J. A Technique for Extracting Small-Signal Equivalent-Circuit Elements of HEMTs[J]. IEICE Transactions on Electronics, 1999, 82(11): 1968-1976.

Article Outline

李织纯, 吕渊婷, 张傲, 高建军. 一种改进的基于110 GHz在片S参数测试的HEMT器件寄生电阻提取方法[J]. 红外与毫米波学报, 2024, 43(1): 85. Zhi-Chun LI, Yuan-Ting LYU, Ao ZHANG, Jian-Jun GAO. An improved method for determination of extrinsic resistances for HEMT devices based on 110 GHz S-parameters on-wafer measurement[J]. Journal of Infrared and Millimeter Waves, 2024, 43(1): 85.