一种大规模光开关阵列驱动控制电路设计方法

1 引 言

光开关阵列是光交换的核心,其功能是实现光信号在不同光路上的快速交换,当光开关达到一定规模后,需要单独控制的开关单元数目非常庞大[1-2],除了光开关芯片本身的设计原理和结构外,控制和驱动电路也影响开关的速度、功耗等特性,进而影响光开关综合性能的发挥[3]。文献[4]和[5]介绍了波导光开关阵列的拓扑结构、大规模硅基光开关阵列结构,介绍了4×4光开关阵列、单片集成光开关的结构及进展,但并没有提供大规模光开关阵列驱动控制电路的设计方法。文献[6]系统研究了大规模光开关阵列的设计方法和实际芯片的制作,很好完成了单个电路单元的制作和测试工作,但缺乏大规模光开关阵列驱动控制电路的整体方案设计,也没有电路和程序设计原理的详细介绍。因此需要对大规模光开关阵列驱动控制电路进行研究。

文章以2000路光开关阵列为控制对象,提出了一种新型的大规模光开关阵列驱动控制电路的设计方法,用于解决光开关速度快而驱动控制电路速度慢的现实问题。首先介绍了2000路光开关阵列驱动控制电路的整体方案,在此基础上,介绍了硬件电路、程序设计的方法,并分析了关键芯片的选型依据,最后研制出200 mm×300 mm的样机,输出控制信号的上升沿和下降沿均小于2 ns。

1 工作原理

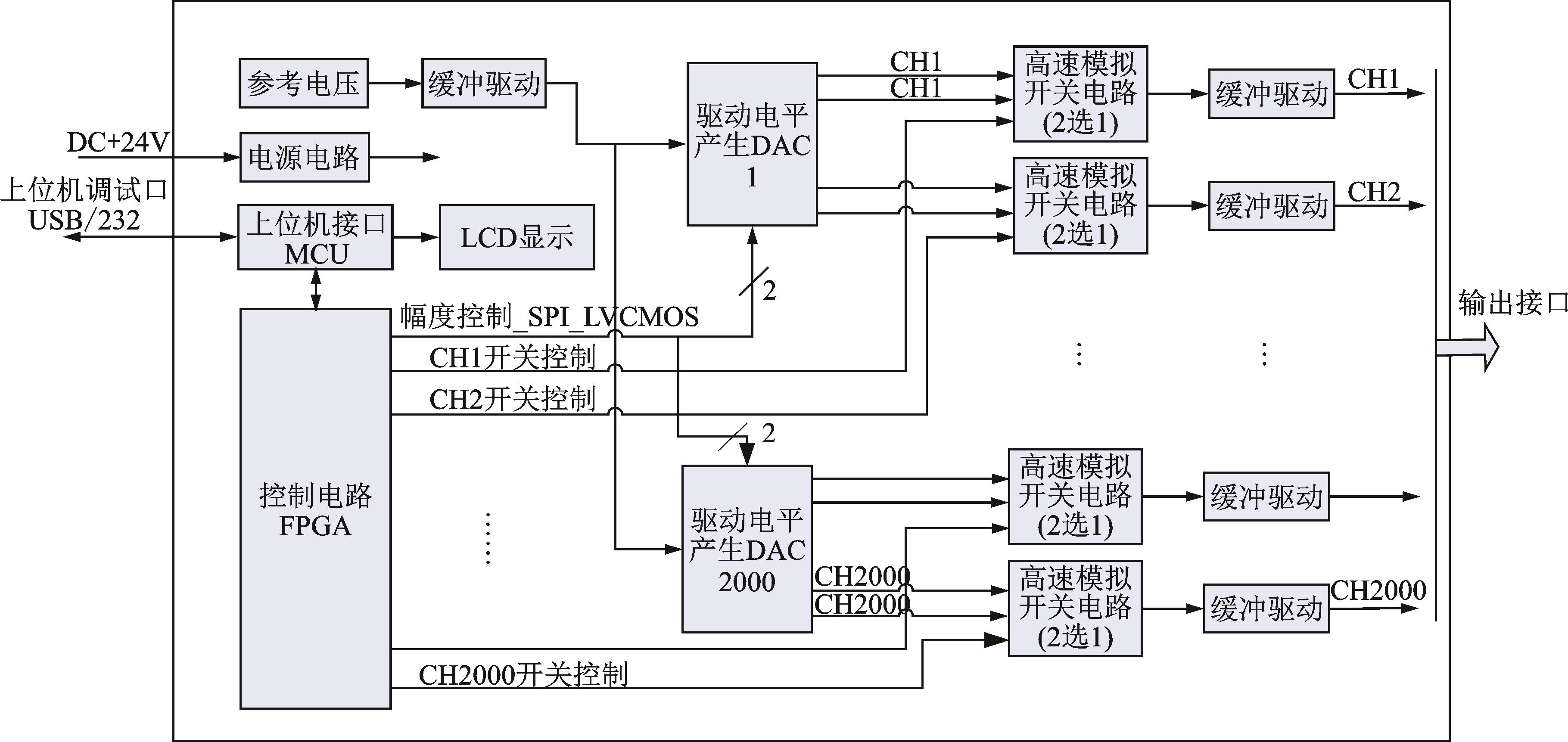

以2000路光开关阵列控制为例,控制方法原理如图1所示,主要由FPGA、驱动电平产生DAC、高速模拟开关电路和缓冲电路组成。

在图1中,FPGA接收上位机的控制指令,输出幅度控制信号给DAC,DAC根据接收到的数字信号转换为对应的高电平、低电平幅度信号,FPGA控制高速模拟开关电路在高、低电平之间不断切换,从而产生脉冲控制信号。因FPGA输出的数字信号是可调节的,经DAC转换后的控制信号高低电也相应地实现了幅度调节。为增强控制信号的驱动能力,在输出端配置了缓冲驱动,用于提高带负载的能力,MCU实现FPGA与上位机的通信控制。参考电压的功能是提供DAC所需的参考电压值,缓冲驱动用于隔离和提高参考电压输出带负载的能力,电源电路提供FPGA、DAC、高速模拟开关电路等所需的不同工作电压,上位机接口的功能是通过通讯接口发送需要输出哪些通道及输出控制信号的幅度,FPGA控制模组接收到控制信号后,输出相应的控制信号,控制信号经输入接口送给控制电路,由控制电路产生对应通道的脉冲信号,通过输出接口输出电脉冲信号。LCD显示单元的功能是实时显示任意时刻哪些通道在输出,输出信号的幅值信息。

2 电路设计与分析

FPGA芯片、数模转换芯片、驱动控制芯片、模拟开关的器件选型及外围电路设计是大规模光开关阵列驱动控制系统电路设计的关键,驱动控制电路如图2所示。

考虑到DAC输出无缓冲且输出信号电流较小,需要加运放电路。运放设计在开关之前还是开关之后,对运放的性能要求不一样,放在开关之前,驱动的是直流电平,对运放的速度要求大大降低,着重考虑运放的驱动能力;放在开关之后,输入运放的是阶跃信号,除要满足驱动能力外,还需考虑运放的建立时间(Settling Time)、大信号时的压摆率(Slew Rate)、带宽等参数,高速运放成本高,功耗大,可选型号有限。因此,如图2所示,设计电路时将运放设置在开关之前。FPGA是控制电路的核心,不仅控制DAC实现信号不同幅度的产生,而且控制高速开关的切换实现脉冲控制信号的输出。FPGA选用EP4CE40F29C6N、DAC选用DAC60096、高速开关选用SN74LVC1G3157。器件选型的合理性关乎整个电路设计的成败,核心芯片的分析及选型如表1所示。

表 1. 核心芯片分析及选型表

Table 1. Table of core chip analysis and selection

|

3 软件设计与分析

大规模光开关阵列驱动控制电路的程序功能包括:可配置每一路驱动信号的高低电平值,可控制每一路脉冲信号的输出或关闭,可配置通信接口的参数,软件设计流程如图3所示。

在图3中,上电初始化主要是对DAC和FPGA进行配置,通信接口参数设置主要实现上位机与控制电路的通讯,配置串口为115 200 bps,1停止位,无校验。通信口检验正常后,默认为指定通道的电平,也可以通过上位机界面设置为全部通道输出,通过上位机还可以设置输入高低电平值、偏置电平值,按更新数据按钮,即完成对指定通道或全部通道电平参数的设置。各通道的状态显示,软件会定时更新各通道状态,包括通道号、高电平值、低电平值等。

4 实验及分析

2 000路光开关阵列驱动控制电路的PCB实物大小约200 mm×300 mm,相当于1张A4纸大小,实物及测试结果如图4所示。

图 4. 光开关阵列驱动控制电路实物及测试图

Fig. 4. Physical object and test diagram of optical switch array drive control circuit

上升沿、下降沿测试使用的仪器是泰克公司的MSO64B ,高低电平及电压调节精度测试使用的是普通万用表。由测试结果可知文章设计的大规模驱动控制电路上升沿1.968 ns,下降沿1.436 ns,高电平在2~3 V之间可调、低电平在0~1 V之间可调,调节精度可达0.01 V。

表 2. 光开关驱动控制电路实验结果

Table 2. Experimental results of optical switch drive control circuit

|

5 结 论

文章提出了一种大规模光开关阵列驱动控制电路的设计方法,使用FPGA控制数模转换器和高速开关实现了高电平、低电平的任意调节,解决了控制信号幅度调节受限、且光开关速度快而驱动控制电路速度慢的技术难题,详细介绍了基于FPGA的电路设计原理和软件设计流程图,并提供了关键芯片的选型依据和具体型号,实现了2 000路光开关阵列驱动控制电路的设计,最后通过实物研制和测试,控制信号切换速度优于2 ns,证实了文章提出的新控制方法的正确性。文中提出的大规模光开关阵列驱动控制电路的设计方法可用于海量数据大容量、低延时传输领域,也可以根据文中提出的设计原理研制通用型光开关阵列驱动控制集成芯片。

[1] 周林杰,陆梁军,郭展志,等. 集成光开关发展现状及关键技术(特邀)[J]. 光通信研究, 2019, 211(1): 13-30.

[2] Mo Z, Wei Y L, Bright V M, et al. High extinction ratio low insertion loss optical switch based on an electrowetting prism[J]. Optics Express, 2020, 28(5): 5991-6001.

[3] 李运涛,陈少武,余金中. 光开关矩阵控制和驱动电路及集成技术的研究进展[J]. 激光与红外, 2005, 35(1): 7-10.

[4] 孙小强,刘崧岳,李鹏飞,等. 硅基光开关及阵列研究进展[J]. 半导体光电, 2022, 43(2): 207-217.

[5] Cheng Daming, Zhang Jihou, Wang Chunxue, et al. Fluorinated photopolymer cascaded MMI-based integrated optical waveguide switching matrix with encoding functions[J]. Optics Express, 2019, 27(9): 12883-12898.

[6]

[7] 樊彦恩,吴彭生,武 帅. 电光晶体光开关的控制及驱动电路研制[J]. 科技创新与应用, 2015, 1(16): 36-37.

[8] Götz-Köhler M, Meddeb H, Gehrke K, et al. Ultrathin solar cell with magnesium-based optical switching for window applications[J]. IEEE Journal of Photovoltaics, 2021, 11(6): 1388-1394.

[9] Ghafari S, Forouzeshfard M R, Vafapour Z. Thermo optical switching and sensing applications of an infrared metamaterial[J]. IEEE Sensors Journal, 2020, 20(6): 3235-3241.

杨鹏毅, 吴洋, 姚宗影, 李鸿高. 一种大规模光开关阵列驱动控制电路设计方法[J]. 光电子技术, 2023, 43(2): 156. Pengyi YANG, Yang WU, Zongying YAO, Honggao LI. A Design Method of Drive and Control Circuit for Massive Optical Switch Array[J]. Optoelectronic Technology, 2023, 43(2): 156.