Incomplete charge transfer in CMOS image sensor caused by Si/SiO2 interface states in the TG channel

1 Introduction

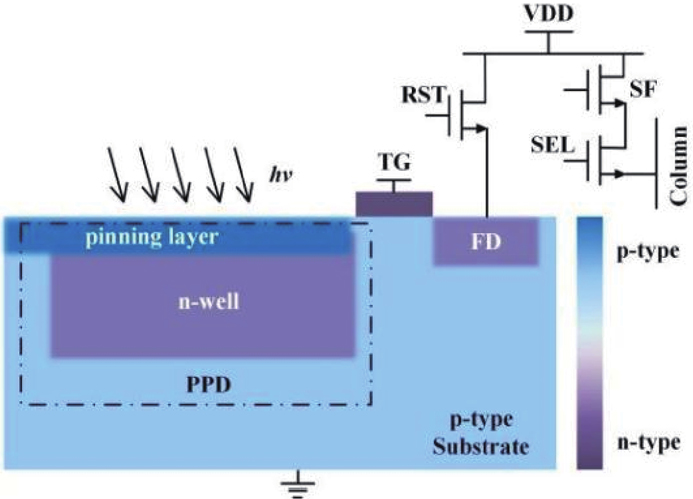

CMOS image sensors (CISs) with pinned photodiodes (PPDs) are widely used in various imaging fields due to their low power consumption, high integration, and high quantum efficiency[1−5]. Charge transfer efficiency (CTE) is a key performance parameter of PPD CISs[6]. Only when the photogenerated charges collected in the PPD are fully transferred through the transfer gate (TG) to the floating diffusion (FD) node can CIS read the complete signal value and achieve a high-quality imaging[7, 8]. However, existing CMOS manufacturing processes usually introduce non-idealities such as potential barriers and interface state traps into the transfer path, making it difficult for CISs to achieve complete charge transfer[9]. Therefore, research in related fields is increasingly focused on exploring the mechanism of incomplete charge transfer.

Thus far, this research can be divided into two main categories based on the factors that cause incomplete charge transfer. The first factor is the presence of potential barriers on the transfer path, which is generated by complicated doping profiles under the TG[6, 10−15]. In Ref. [6], Serena Rizzolo in France investigated the influence of pixel design on image lag by focusing on two different aspects which impact the charge transfer. In Ref. [10], Raffaele Capoccia in Switzerland proposed a physics-based compact model of the pinned photodiode combined with the transfer gate. In Ref. [11], Cui Yang in Xidian University proposed and investigated a novel CMOS image sensor pinned photodiode pixel, named as O-T pixel. In Ref. [12], Xiuyu Wang in Tianjin Univeristy proposed an analytical model for quantifying the charge transfer potential barrier in pinned photodiode CMOS image sensors. In Ref. [13], Uzma Khan in India reported the full well capacity and the pinned photodiode capacitance of four-transistor pixels in a CMOS image sensor to be dependent on the potential barrier offered by transfer gate. In Ref. [14], Lu Liu in National University of Defense Technology proposed an analytical model of the potential barrier for the pinned photodiode combined with the transfer gate. In Ref. [15], Congzhen Hu in Xi'an Jiao Tong University proposed physical-based model to characterize the whole charge behavior characteristics of the pinned photodiode when employing the thermal diffusion, self-induced drifting, and thermionic emission mechanisms together. The second factor leading to incomplete charge transfer is the spill back effect under high illumination. The physical mechanism underlying this effect was investigated in Ref. [16].

Silicon devices inevitably suffer from interface state traps[17]. In 2007, Boyd Fowler proposed a conjecture: There are two reasons for image lag, one is the potential barrier on the transfer path, and the other is the trap in the TG channel[18]. In 2012, Bonjour et al. accurately distinguished the incomplete charge transfer caused by potential barriers and traps in the TG channel, which confirmed the influence of interface state traps on charge transfer[19]. Specifically, under low illumination, the number of photogenerated electrons collected in the PPD decreases[20], and the proportion of electrons that cannot be transferred to the FD node in the total number of photogenerated electrons will increase. This leads to more obvious degradation of the imaging quality of CISs under low illumination[9].

However, Bonjour et al. only confirmed the effect of interface state traps in the TG channel on charge transfer, they did not provide any analytical model for CISs to quantify the incomplete charge transfer caused by interface state traps in the TG channel. The mechanism of incomplete charge transfer caused by interface state traps is still unclear. Without a quantitative model as a guide, the experimental findings remain limited to the specific experimental conditions. Therefore, it is particularly necessary to establish an accurate physical model for the incomplete charge transfer caused by interface state traps in the TG channel.

This paper proposes a physical model for quantifying the incomplete charge transfer caused by interface state traps in the TG channel. First, the value of the boundary trap energy level is determined by calculating emission time constants of different trap energy levels based on Shockley-Read-Hall (SRH) theory and comparing them with the time of the TG to the off state. Then, according to the small injection theory, the quasi-Fermi level is approximated to the Fermi level, and the relationship between the probability of electrons occupying the trap energy level and the Fermi level is established based on the Fermi-Dirac statistical distribution. Next, an explicit two-dimensional expression for the number of untransferred charges associated with the trap state density and trap energy level distribution is established, and the variation rules of the number of untransferred charges and charge transfer efficiency are given when the trap energy levels follow different distributions, particularly under low illumination. Finally, the proposed model is verified using technology computer-aided design (TCAD) simulations.

2 Mathematical model

A typical four-transistor pixel structure, including PPD, TG, and FD node, is shown in

where

2.5 Determination of boundary trap energy level Et0

To further explore the restriction mechanism of interface state traps on charge transfer, the core step is to explain the behavior of interface state traps in the TG channel during charge transfer, to capture and release carriers.

Fig. 2. (Color online) VTG time sequence diagram, semiconductor energy band diagram, and charge trapping effect during charge transfer. (a) Time sequence diagram of VTG during charge transfer. (b) Energy band diagram of the semiconductor in the TG region at VTG-Low. (c) Process of electron capture by interface states in phase Ⅰ. (d) Energy band diagram of the semiconductor in the TG region at VTG-High. (e) Process of electron emission by interface states in phase Ⅲ.

where n is the electron density of Si semiconductor,

Table 1. Parameters of the mathematical model.

|

Eq. (3) indicates that the emission time constant of the trap energy level is related to the position of the trap energy level in the band gap. An energy level far from the conduction band, also known as the deep level trap, has a large emission time constant. Therefore, the electrons trapped by the deep level traps cannot be emitted into the conduction band during TG closure, as shown in

During charge transfer, the semiconductor under the TG will generate an electron inversion layer to form the conductive channel. When the threshold inversion point is reached, the electron concentration in the channel is equal to the hole concentration of the p-substrate in

2.6 Model for quantifying incomplete charge transfer caused by different trap energy level distribution

After the TG is turned off, the number of charges stored in interface states, with a continuous distribution from the band gap center

where

where

In this way, based on the relationship between

Eq. (1) can be further written as Eq. (9). Thus, the

In the actual manufacturing process, owing to fluctuations in CMOS technology, for the same pixel design, the position of the trap energy level is not always a single constant[23, 24]. In addition, it is demonstrated in Ref. [25], that the common trap energy level distribution includes Gaussian (as shown in Eqs. (10) and (11)) and exponential distributions (as shown in Eqs. (12) and (13)).

In the Gaussian distribution, the trap energy level is not equal to the intrinsic Fermi level and is continuously distributed in the silicon band gap. Moreover, the center of the trap energy level deviates from the center of the silicon band gap, as indicated in Eq. (10). E0 is the average value of the Gaussian distribution, and it ranges from 0 to 1.12 eV. ES is the variance of the Gaussian distribution, and it is slightly smaller than this band gap width. When Eq. (10) is inserted into Eq. (7), NTrapped exhibiting a Gaussian distribution of the trap energy level can be further expressed as NTrapped-Gaussian (Et, Nt) in Eq. (11).

In the exponential distribution, the trap energy level is not equal to the intrinsic Fermi energy level. The center of the trap energy level also deviates from the center of the silicon band gap, as indicated in Eq. (12). By substituting Eq. (12) into Eq. (7), NTrapped exhibiting an exponential distribution of the trap energy level can be further expressed as NTrapped-Exponential (Et, Nt) in Eq. (13).

3 Simulation results

This study verifies the model in detail by using Gaussian trap energy level distribution, exponential trap energy level distribution and 32 sets of measured trap energy level distributions, which are supplied by Chongqing Optoelectronics Research Institute, the relationship between trap energy level Et and trap state density Nt as shown in

Fig. 3. (Color online) Different trap energy level distributions. (a) 1−8 sets of measured distribution data of Si/SiO2 interface state. (b) 9−16 sets of measured distribution data of Si/SiO2 interface state. (c) 17−24 sets of measured distribution data of Si/SiO2 interface state. (d) 25−32 sets of measured distribution data of Si/SiO2 interface state.

To verify the mathematical model proposed in this paper, simulations were conducted on the Synopsys Sentaurus TCAD 2018. First, process simulation design was carried out in the Sprocess module in TCAD with reference to the advanced CMOS process flow. This step acquired process simulation files with doping, material and boundaries information, etc. After that, the files were imported into the Sdevice module in TCAD for physical characteristics simulation. By adding lighting models, trap models, and pixel timing spice models, the 4T pixel model is equipped with various physical characteristics. Finally, we used the 4T pixel model to simulate the number of untransferred charges when the duration of the TG falling edge is equal to the emission time constant of electrons.

The CIS PPD 4T pixels are simulated by a 0.18 μm CIS technology, and the structural parameters of the simulation are listed in

3.5 Specific curve results of NTrapped and CTE changing with E0 under Gaussian and exponential distributions

Fig. 4. (Color online) Variations in NTrapped with the mean value E0 under Gaussian and exponential distributions.

Fig. 5. (Color online) Variations in CTE with the mean value E0 under Gaussian and exponential distributions.

3.6 Specific curve results of NTrapped and CTE changing with Es under Gaussian and exponential distributions

Fig. 6. (Color online) Variations in NTrapped with different variances ES under Gaussian and exponential distributions.

Fig. 7. (Color online) Variations in CTE with different variances ES under Gaussian and exponential distributions.

3.7 Specific curve results of NTrapped and CTE changing under measured trap energy level distributions

In order to reflect the relationship between NTrapped and trap energy level distributions, trap charge density is calculated as Eq. (14), when the measured trap energy level distributions in

4 Conclusions

In summary, an analytical model for quantifying the incomplete charge transfer caused by Si/SiO2 interface state traps in the TG channel under low illumination has been established for the first time. This model can predict the variation rules of the number of untransferred charges and charge transfer efficiency when the trap energy level follows different distributions. The model has been verified with TCAD simulations, and the consistency between model and simulation results proves the accuracy of the proposed model in this paper. The proposed model provides beneficial theoretical guidance for the circuit design and analysis of CISs.

[8] FossumE RCharge transfer noise and lag in CMOS active pixel sensors. IEEE Workshop CCD’s AdvImage Sensors200311

[17] XuYFundamental characteristics of a pinned photodiode CMOS pixelPh. D. dissertation, Dept. Microelectron. Comput. Eng., Delft Univ. Technol., Delft, the Netherlands2015

[18] FowlerBLiuXCharge transfer noise in image sensorsInternational Image Sensor Workshop (IISW)20072

[21] LiuEZhuBLuoJThe physics of semiconductorsBeijing: House of Electronics Industry201111

Article Outline

Xi Lu, Changju Liu, Pinyuan Zhao, Yu Zhang, Bei Li, Zhenzhen Zhang, Jiangtao Xu. Incomplete charge transfer in CMOS image sensor caused by Si/SiO2 interface states in the TG channel[J]. Journal of Semiconductors, 2023, 44(11): 114104.