读出电路开窗技术研究

0 引 言

红外焦平面阵列(Infrared focal plane array, IRFPA)在工业、**[1]和医疗[2]等领域被广泛应用。近年来,读出集成电路(Readout Integrated Circuit, ROIC)作为红外焦平面的重要组成部分,发展极其迅速[3]。1999年,Donald·Reago等提出了第三代红外焦平面的概念[4]。其中大面阵、高帧率[5]和数字化[6-7]是读出电路的发展方向。在大面阵的情况下,为了得到高帧频且不增加带宽和功耗[8],读出电路开窗技术被采用。

读出电路开窗技术又称感兴趣区域(Region of Interest,ROI)读出或随机开窗口读出。读出电路任意开窗技术是指仅选通像元阵列的一部分来进行数据读出。该技术通过降低数据总量的方式,在不增加带宽和功耗的前提下提高了帧频。

1 读出电路开窗技术

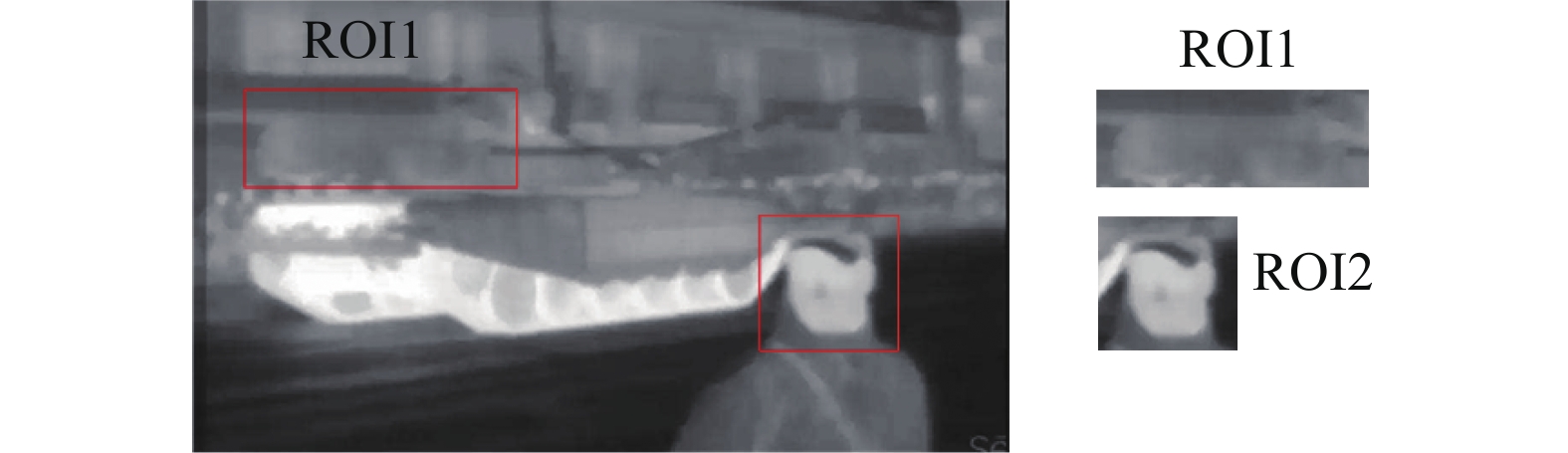

读出电路开窗技术具有较多的应用场景。在大面阵红外焦平面上,如图1所示,用户可通过开窗技术重构图像大小帮助观察感兴趣的区域或快速导出指定区域的信号[9]。此外,该技术还可应用于目标跟踪或模式识别中[10]。

读出电路开窗的目的之一是在不增加带宽和功耗的前提下提高帧率。读出电路开窗后每一帧所需读出的数据量显著降低,减少了数据读出的时间,从而使得帧频得以提高。

在开窗情况下,设开窗的窗口形状为正方形,当窗口尺寸变化时,需要读出的总数据量X的变化式为:

式中:m为窗口尺寸;

若ADC位数为15位,像元面阵大小为1024×1280,当开窗的窗口尺寸逐渐缩小时,需要读出的总数据量和数据读出所需时间的关系如图2所示。

图 2. 总数据量和读出时间与窗口尺寸的关系

Fig. 2. Relationship between total data volume and readout time and ROI size

由此可以看出,随着窗口尺寸的减小,读出的总数据量和数据读出所需的时间都明显降低。

在实际应用中,受像元阵列积分时间的影响,读出电路完成一帧数据读出所需的时间并不完全等于上述的数据读出理论时间,即电路的帧频与理论帧频存在差异。当电路处于边积分边读出(Integration while read, IWR)模式下时,电路的帧频、数据读出时间及像元积分时间的关系如公式(4)所示。若数据读出时间小于像元的积分时间,则电路的帧频主要受限于积分时间;若数据读出时间大于像元的积分时间,则电路的帧频主要被电路的读出时间所限制。

当电路处于先积分后读出(Integration then read, ITR)模式时,电路的帧频可表示为:

式中:

设面阵大小为1024×1280,积分时长为5 ms,每读出一位数据所需时间按照2 ns计算,帧频与不同窗口尺寸的关系如图3所示。

从图中可以看到,电路在IWR模式下,窗口尺寸减小时,帧频呈现明显的上升趋势。然而,随着当窗口尺寸进一步减小,数据读出时间减小,当读出时间小于像元的积分时长后,电路完成一帧所需的时间主要取决于电路的积分时间,所以电路的帧频不再降低,而是维持在200 Hz;电路在ITR模式下,随着窗口尺寸的降低,电路的帧频逐步提升,在窗口读出时间低于积分时间后,电路的帧频上升趋势逐渐减缓,最终趋近于200 Hz,此时窗口尺寸为1×1。因此,开窗口技术能有效降低读出的数据总量,对提高帧频有显著的作用。

2 读出电路开窗架构

读出电路开窗技术自提出后,由于其对帧频具有明显的提升作用及未来在目标跟踪等方面的应用前景,受到了很大的关注,国外的各大公司也各自推出了具有开窗口功能的红外探测器。

目前国内外电路级别的开窗电路架构有很多种,从读出方式可以分为两类:异步读出模式和同步读出模式。异步读出模式直接从译码器获得读出的地址,所以其可以自由读出任意不连续的地址,其中的代表架构为格雷码译码器架构;同步读出模式只获取初始地址,后续读出的地址仅与时钟相关,因此该模式只能读取连续的地址,其中应用较多的架构为单像元控制架构和子阵列架构。

异步读出模式中,由于采用译码器直接输出地址,会导致竞争冒险现象。图4为一种由门电路组成的3-8译码器,在输入的值A、B、C不同时,信号通过的门数量不同,如输入C到输出Y7需要通过3个门电路,而到输出Y0只需要通过2个门电路,所以信号的时序会产生差异,从而导致竞争冒险现象。

目前主流的红外探测器面阵大多在几百行,甚至上千行,若采用译码器结构来实现,则门电路的数量大大增加,信号通路长度的不一致的现象将被放大,导致更为严重的竞争冒险。如图5(a)所示,RS信号为行选信号,此时RS<1>和RS<2>两个信号出现竞争冒险现象,将会有两行像元同时选通,导致读出出错。所以,在该架构中,需要在各行、列中增加冗余的时间,以减小竞争冒险现象对电路的影响,但这意味着电路的读出时间变长,如图5(b)所示。

同步读出模式则很好地解决了竞争冒险的问题,如图5(c)所示。同步读出模式由于只获取初始地址,后续读出的地址仅与时钟相关,读出的地址与时钟上升沿对齐,因此前级电路产生的竞争冒险会被消除。

2.1 格雷码译码器架构

格雷码译码器架构采用异步读出模式,是目前红外焦平面阵列中使用最为普遍的一种架构。格雷码译码器架构的开窗优点是在小面阵时电路结构简单、版图占用芯片面积小[11],同时在窗口位置或大小发生变化时,电路恢复读出所需的时间极短,仅为组合逻辑电路的延时。计数器采用格雷码计数器,由于格雷码相邻两位只改变一位的特性,相对于普通二进制计数器而言,格雷码计数器更加的稳定。图6为典型的格雷码译码器架构,由译码器模块和控制电路组成。控制电路主要由格雷码计数器构成。处理器将窗口参数加载到格雷码计数器中,以定义窗口大小和位置[11]。系统通过行同步信号启动行格雷码计数器,每当行格雷码计数一次就会启动列格雷码计数器,当列格雷码计数器计数到窗口结束位置时,行格雷码计数器计数一次,行、列计数器的输出结果通过译码器选通各行各列,从而使阵列的每一像元单元的信号得到输出。

该架构具有其固有的优点,即当译码器的输入变动时,可以自由的选通任意像元[12]。但是当面阵规模大时,译码器位数较多,会导致译码器的设计复杂,且不同的面阵规模下译码器电路差异很大,所以电路需要重新定制化设计,增大了工作量。

2.2 单像元控制架构

单像元控制架构采用异步读出模式,该架构依靠像元内存储的控制字提供初始地址。

单像元控制字架构在保证最小窗口尺寸的同时,将电路放置在像元内部,避免了竞争冒险现象,同时采用了模块化设计,在面阵发生变化时,扩展简单。图7为单像元控制字的架构示意图,相比于格雷码译码器架构来说,单像元架构在每一个像元内都有存储单元和控制电路。Rafael等人提出的一种存储单元和控制电路,除去绿色虚线内的像元积分电路外,在右侧新增了红色虚线内的用于存储控制字的寄存器,用于“编程”的移位寄存器以及用于控制像元开启的门电路[13],如图8所示。

该方案选择在每一列的第一行的像元中的寄存器置1。在数据读出时,对每个像元逐个验证,控制字为0跳过,控制字为1读出。此时每列的第一个像元读出,全部读出完成后,移位寄存器向下移位,读取第二行,此时移位寄存器内只有一位1,其余为0,所以每列只会有一位读出。结束信号由计数器控制,当读出至最后一行时,结束读出。

以Rafael等提出的电路为例,单像元控制字架构在保证最小窗口尺寸的同时,将电路放置在像元内部,增加了电路的可扩展性,同时避免了竞争冒险现象。但是在像元内额外增加电路,占据像元内空间,考虑基本的直接注入型像元结构仅需要4个MOS管,而增加的额外电路,以基础的传输门电路组成的触发器来计算,需要34个MOS管,这将导致像元面积缩小非常困难;其次,该架构采用了大量的控制字控制像元,在窗口位置或大小发生变化时,控制字需要重新写入,耗费时间较长。

2.3 子阵列控制架构

为了降低单像元控制字架构对于像元内面积的占用,以及降低在窗口发生变化时,电路恢复读出所需的时间,同样采用异步读出模式的子阵列控制架构被提出。该架构的原理是将一组像元集合视为子阵列,同时对其进行标记,如图9所示。此架构要求在每一组子阵列中放置寄存器和逻辑电路,当电路读出时,对每组像元集合中寄存器中的值进行扫描,标记有效的读出,无效的则跳过。

图10是Schrey等提出的一种控制模块和存储单元[14],该方案将控制字提前写入存储单元中,需要数据读出的写入1,不需要读出的写入0。在数据读出时,对每个像元集合逐个验证,控制字为0跳过,控制字为1读出。由于可以自行规定扫描的顺序,方案可以做到多窗口不同尺寸,不同方向的读出。

在该方案中,子阵列大小为32×32,控制模块和存储单元由3个触发器和5个“与”门组成,以基础的传输门电路组成的触发器来计算,控制模块和存储单元额外增加了68个MOS管。若像元为直接注入型,则每个像元中平均需要额外增加0.26个MOS管。相对于单像元控制字架构而言,电路占用的像元面积大大减小;同时降低了控制字的数量,从而在窗口位置或大小发生变化时,电路恢复读出所需时间减小。但是,该架构的窗口的最小尺寸等于子阵列的大小,若想继续降低窗口的最小尺寸,则需要进一步减小子阵列的大小,此时控制模块和存储单元在像元电路中占用的面积就会随之增加,像元的面积则会进一步增大。当子阵列大小减小到1×1时,子阵列架构占用的像元面积与单像元控制字架构相同。

2.4 各架构比较

格雷码译码器架构较为常用且在小面阵上有较为优异的表现,但是当面阵较大时,会产生较为严重的竞争冒险现象,同时在面阵尺寸发生变化时,电路需要重新定制化设计,增加工作量且可扩展性相对较差。

单像元控制字架构则在保证最小窗口尺寸为1×1不变的情况下,避免了竞争冒险现象,而且增加了电路的可扩展性,但该方案像元尺寸很难缩小,同时在窗口尺寸或位置发生变化时,控制字都需要重新写入,占用时间较长。

子阵列控制字架构减小了对像元面积的占用,减少了控制字的数量,在窗口尺寸或位置发生变化时,控制字重新写入的时间相对于单像元控制字架构有所降低,但其最小的窗口尺寸也随之增加。

因此,文中提出了一种基于行列控制字读出电路开窗架构,该架构采用模块化设计,易于扩展,在不占用像元内部的面积下,实现了最小窗口尺寸1×1,并且不存在竞争冒险现象,同时在窗口位置或大小发生变化时,电路恢复读出所需时间不会明显增加。

3 读出电路开窗架构及电路设计

3.1 读出电路开窗架构

文中提出的基于行列控制字的读出电路开窗架构如图11所示。该架构与同步读取模式类似,读出的起始位置取决于存储在行列上的控制字。此时为像元(N-3,3)被选通时电路的状态。

该方案由信号处理电路和控制子电路组成,其中控制子电路由移位寄存器和存储器组成。控制电路接收并处理由串行外围接口(Serial Peripheral Interface,SPI)输入的数据,并将数据进行预处理,然后生成控制字和控制信号并传递给控制子电路。控制子电路存储控制字于窗口的起始行和列,当电路读出时,子电路读取存储器内的数值,从而实现不同起始位置的读出,控制字向后依次移位依次读出各行各列,结束位置由控制电路产生,实现任意大小的窗口。

该架构通过分别控制行和列来实现选通。当只选通一行和一列时,只有一个像元被选通,实现了最小窗口尺寸1×1;同时该架构将控制电路设计在像元阵列外围,不占用像元内部的面积;采用控制子电路模块来分别控制每行和每列,可以重复使用,所以在面阵尺寸发生变化时,电路不需要重新定制化设计,易于扩展;另外,没有采用组合逻辑电路,不存在竞争冒险现象;同时,控制字的数量被缩减,控制字写入的路径也被较好的缩短,因此在窗口位置或大小发生变化时,电路恢复读出所需的时间也相对较少。

3.2 窗口切换速度分析

读出电路开窗的一个重要应用方向是目标搜索和跟踪。当目标的位置发生改变时,读出电路的窗口位置也应该迅速随之改变。当窗口的位置或者大小改变时,电路需要一段时间来恢复正常读出,我们称之为称为窗口切换速度,窗口切换速度越快,则电路对实际应用的影响越小。

在格雷码译码器架构中,窗口切换速度很快,其所需的时间仅为组合逻辑电路的延时,所以在此忽略不计。采用同步读取模式的三种架构都需要写入控制字,所以需要考量控制字的写入时间。

在单像元控制字架构中,由于在每一位像元中都存在控制字,当窗口的位置或者大小改变时,需要重新写入每一位控制字,需要时间较长,产生控制字写入时间

式中:M为面阵行数;

在子阵列控制字架构中,采用对子阵列编码的逻辑,减少了控制字的数量,降低了控制字写入时间,控制字写入时间

式中:

文中所提出的行列控制字架构方案产生的控制字写入时间

式中:

单像元控制字架构采用了每个像元都存储控制字的方案,除了需要将控制字逐行存储在预定位置外,还需要额外的时间

下面以面阵大小1024×1280,子阵列大小32×32为例,对比三种方案的控制字写入时间,如图12所示。考虑到实际情况中不同电路需要的额外时间

从图中可以看到,控制字写入时间最长的为单像元控制字架构,由于像元内的控制字需要逐一改变,所以其需要遍历各行,需要时间最长为

对比3种架构,在不考虑时间

3.3 读出电路开窗电路设计

此节将提供一种基于文中所提出的行列控制字架构的开窗电路实现方案,并展示了该实现方案具体的工作流程及工作时序。

控制子电路的设计是本架构的重点,控制子电路由移位寄存器和数据存储器组成,其中移位寄存器和数据存储器均为D触发器(DFF)。如图13所示,信号ROW_ED无效时,当前级移位寄存器的输入由前一级移位寄存器的输出RS

当信号ROW_ED有效时,无论其他信号是否有效,在信号CLK_RS上升沿之后,所有移位寄存器都将被复位,并关闭电路的输出。最终,通过信号ROI_RS和信号ROW_ED共同控制窗口的读出。同时信号ROW_WIR和信号ROW_WIR的上升沿需要延迟于CLK_RS的上升沿,确保信号可以成功建立。

ROI_RS处于高电平时,存储在数据存储器中的数据被写入移位寄存器的输入,以确定窗口的开始位置。当读出电路读出窗口数据之前,需要将控制字分别写入数据存储器中。

图14展示了完整的行控制字写入过程。如图14(a)所示,首先在第一个移位寄存器输入信号ROI_S,通过移位寄存器移位该信号,直至窗口的第一行对应的位置,如图14(b)所示。当控制字移动到新状态的起始位置时,存储在数据存储器中的数据在信号ROW_WIR的作用下写入控制字至寄存器,如图14(c)所示。写入完成后,复位所有移位寄存器,行控制字写入完成,如图14(d)所示。行控制字的写入时序如图15所示,其中信号ROW_WIR与信号RS<3>存在延时,以确保信号可以成功的被写入寄存器。该方案在读出时先选通一行,然后逐次选通各列,由于行列的选通的逻辑相同,所以文中只详细介绍行选逻辑及时序。

该方案的行选工作逻辑如图16所示,如图16(a)所示,开始信号ROW_RS输入,将寄存器内数据写入移位寄存器,如图16(b)所示,选通窗口第一行,然后移位寄存器逐级向下移位,如图16(c)所示,逐行选通,当选通至窗口最后一行时,结束信号ROI_ED输入至移位寄存器,如图16(d)所示,复位移位寄存器,行选结束。

图17为行选过程的时序图,其中信号ROI_ED与信号RS

3.4 版图设计与仿真

由于本架构需要在电路外围增加控制电路,为了确定额外增加的控制电路所占用的面积,文中在0.18

为了进一步验证该方案的可行性,搭建了一个像元面阵大小为16×16的电路,其中规定窗口大小为12×12,起始位置为(3,3),实验得出波形如图19所示。行选产生信号RS<3>~RS<14>,读出3~14行,与预设条件一致。读出预定区域内的图像,电路工作正常。

同时,为了验证电路在大面阵时的工作情况,设计了一个1280×1024的像元阵列,通过寄存器模拟像元,并将每个模拟像元对应的行列值相加存储在寄存器中以模拟不同位置不同像元的输出。设置窗口大小为733×179,起始位置为(101,211),读取不同像元的输出值,以读取的值表示该像元在图像中的灰度值,并将其映射为彩色图像。仿真结果如图20所示,上图为全面阵的图像,其中的黑色框为待读出的开窗区域,下图为读出的窗口数据图像,可以看到该电路正确读出。其中仿真设定行时钟周期为30 ns,实际窗口切换时间为3032.4 ns,公式(8)计算所需时间为

4 总结与对比

文中提出了一种基于行列控制字的新开窗架构,并提供了一种电路实现方式。表1对比了各个架构。

表 1. 不同方案的对比

Table 1. Comparison of different schemes

|

格雷码译码器架构理论最小窗口可以达到1×1,目前美国indigo公司产品ISC0403最小尺寸为4×4,该架构采用异步读出模式,存在竞争冒险的风险,而且不同面阵大小电路需要重新定制化设计。

采用同步读出模式的子阵列架构与单像元控制字架构不会产生竞争冒险现象,但是在像元内增加了晶体管,导致像元尺寸难以缩小。

文中提出的架构采用同步读出模式,避免了竞争冒险现象,同时该架构采用了重复模块,在面阵大小变化时不需要重新设计,可扩展性相对较好;相对于子阵列架构来说,该方案的最小窗口尺寸达到1×1,而且将控制电路设计于面阵外围,没有占用像元面积,使得像元尺寸容易缩小;相对于单像元控制字方案,在同样的最小窗口尺寸下,没有占用像元面积,而且大大提高了窗口切换速度。

[1] Liu Wu, Sun Guozheng. The status quo, developments and military application analysis of the multi-color ir focal plane arrays[J]. Infrared Technology, 2004, 26(3): 1-4,10.

[2] Zheng Yingqi, Chen Yongjie, Zhu Xiaozhang. Research progress of near-infrared organic photovoltaic photodetectors[J]. Acta Polymerica Sinica, 2022, 53(4): 354-373.

[4] Choi J, Han S W, Kim S J, et al. A spatialtempal multiresolution CMOS image sens with adaptive frame rates f moving objects in the regionofinterest[C]IEEE International Solidstate Circuits Conference. IEEE, 2007.

[9] Deng T Q J, Shen K, Ruan A W, , et al. Design of a control circuit for a user reconfigurable ROIC for IRFPA applications[J]. COMPEL International Journal of Computations and Mathematics in Electrical, 2010, 29(2): 327-337.

[10] Liu X, Zhang M, Van der Spiegel J. A low power multimode CMOS image sens with integrated onchip motion detection[C]IEEE, 2013: 24162419.

[11] Liu Qi, Xia Xiaojuan, Xu Shen. Design of 640 × 512-25 μm multi-function infrared readout circuit[J]. Aero Weaponry, 2019, 26(2): 90-95.

[12] Doran R W. The gray code[J]. Journal of Universal Computer Science, 2007, 13(11): 1573-1597.

[13] Castro R D, Castillo S M, Juárez R, et al. Advanced region of interest function f image senss: US. Patent 9, 979, 904[P]. 20180522.

[14] Schrey O, Huppertz J, Filimonovic G, , et al. A 1 k/spl times/1 k high dynamic range CMOS image sensor with on-chip programmable region-of-interest readout[J]. IEEE Journal of Solid-State Circuits, 2002, 37(7): 911-915.

[15] Kataria H, Asplund C, Lindberg A, et al. Novel highresolution VGA QWIP detect [C]SPIE, 2017, 10177: 529536.

Article Outline

崔长坤, 陈楠, 钟昇佑, 张娟, 姚立斌. 读出电路开窗技术研究[J]. 红外与激光工程, 2022, 51(11): 20220100. Changkun Cui, Nan Chen, Shengyou Zhong, Juan Zhang, Libin Yao. Research on ROI readout technology of ROIC[J]. Infrared and Laser Engineering, 2022, 51(11): 20220100.